# EDN電子技術設計

EDN-Taiwan 2019年7月

# LoRa技術——低功耗滿足長距離傳輸

利用低功耗 SAM R34 SiP 元件開啟您的下一個 LoRa 的專案

利用我們全新高整合度的 LoRa 系統級封裝 (SiP) 系列元件,加速您的下一個設計。 這些新元件具有超低功耗 32 位元微控制器 (MCU)、sub-GHz RF LoRa 收發器和軟 體協議堆疊,適用於各種長距離的低功耗 IoT 應用,這些應用需要小巧封裝設計和 多年的電池使用壽命。

借助這一全新的元件系列,您可以輕鬆著手下一個設計,透過將應用程式碼與我們的 LoRaWAN™ 協議堆疊相結合來輕鬆運行您的設計。利用 ATSAMR34-XPRO 開發板還可快速進行原型設計,該開發板獲得 Atmel Studio 7 軟體發展套件 (SDK)的支援。該開發板經美國聯邦傳播委員會 (FCC)、加拿大工業部 (IC) 和無線電設備指令 (RED) 認證。SAM R34 SiP 元件支援從 862 到 1020 MHz 的全球 LoRaWAN工作頻率,只需一個元件便可用於多個地理位置。

# 主要特性

- · 業界低功耗 LoRa 技術的 SiP

- · 經驗證的 LoRaWAN 軟體協議堆疊

- 小巧封裝

#### 聯繫信息

Microchip 台灣分公司

電郵:rtc.taipei@microchip.com 技術支援專線:0800-717-718

聯絡電話:

新竹 (03) 577-8366

高雄 (07) 213-7830

台北 (02) 2508-8600

microchip.com/SAMR34

# EDN電子技術設計

EDN-Taiwan 2019年7月

# 砂光子步入 黃金時代

人工智慧是否會進入測試產業?

分析主流SiC MOSFET和 GaN HEMT元件

解析顯示技術演進與參賽者之爭

電源完整性還有新招?

耗蝕性雷射釋放材料應用於RDL優先 扇出封裝優勢

# EDN電子技術設計

足不出戶,與技術大咖互動交流!

不受時空束縛,線上!行動!

www.edntaiwan.com/webinars

掃碼登入參與線上研討會!

# 線上研討會精彩重播

#### 為什麼選擇智能門級驅動光電耦合器?

參加本次網路研討會,得以瞭解智慧門級驅動光電耦合器如何將這些功能集成到IC中,以幫助減少元件數量,節省空間,降低成本和時間。

# **<b>№** BROADCOM®

#### 光電耦合器發光二極體的性能劣化 - 事實還是虛構?

線上研討會一開始會介紹該公司,博通本身簡介, 然後會講解關於光耦合器技術的細節,如絕緣等級和老化機制,靜電放電和高壓浪湧的影響和發光二極體的長期操作時的性能劣化表現。最後,我們來看看目前博通擁有的隔離產品組合和一些關鍵的新產品介紹

#### 採用ADI REM交換器的即時POWERLINK

隨著對更高效率和更高功率密度解決方案的需求增加,隔離式閘極驅動器的時序要求也隨之提高。 本線上研討會將闡述關鍵的時序要求,如傳播延遲和驅動強度,並展示應用中的指標測量方法

#### 超越一切可能™

#### SoC 安全需要主動防護

參加本次網路研討會,您將瞭解:SoC 開發人員關注的常見安全威脅以及如何防範這些威脅;可信執行環境 (TEE) 的類型和典型的 SoC 安全實現;保護 SoC 所需的關鍵構建模組;完整的安全 IP 解決方案,可防禦不斷演變的威脅。

# SYNOPSYS°

#### 高性能慣性感測器助力運動物聯網

高度可靠、智慧和互連感測器的可用性推動工業效率邁上新臺階。新一代工業感測器尺寸更小、性價比更高,支持厘米級定位精度;實現運動物聯網[IoMT]

#### 超越一切可能™

#### 時效性乙太網路在汽車電子以外的應用

參加本次網路研討會,瞭解從基於優先順序的 IEEE 802.1Q 到時效性網路開發的TSN 標準功能。 瞭解 TSN 如何影響整個網路生態系統以及如何使用乙太網路 TSN IP 實現你的 SoC。 SYNOPSYS®

# 目錄Contents

# 10 封面特寫

# 矽光子步入黃金時代

矽光子一直是一項極具吸引力的 技術。經過數十年的研發,矽光 子產品在過去幾年中已經進入市 場並後入實際應用。

# 04 EDN評論

人工智慧是否會進入測試產業?

# 06 技術脈動

- 分析主流SiC MOSFET和GaN HEMT元件

- NIWeek 2019現場直撃

# 相關報導

# 當延遲線記憶體出現致命 缺陷…

延遲線(delay line)元件是電腦記憶體的早期形式(約1960年代之前)。時至今日,它雖然已經過時,但我想起自己曾經參與一項有關的計劃。該計劃雖然最終宣告失敗,但即使如今思考當時失敗的原因也可能相當有幫助。

https://bit.ly/2IGZQLr

# 這7款USB示波器,哪一 款適合你?

從入門級到專業級,基於PC的USB示波器種類越來越多。具有USB連接功能、基於PC的示波器可提供各種性能水準,而且價格低廉。從入門級到具高頻寬的採樣示波器,以及支援更多功能的新版本不斷上市。本文從中選出了七款,看看哪一款最適合你?

https://bit.ly/2xbAM8T

# 您也可以免費訂閱!

立即掃描訂閱

如果您已訂閱,請儘快續訂以確保繼續收到雜誌。

# 只需發郵件至:

eMedia.Support@AspenCore.com, 註明「雜誌續訂」及您的讀者編號。

備註:僅符合條件的業內人士可獲得免費贈閱,出版方保留最終決定權。

# 目錄Contents

# 16 技術縱橫

- 解析顯示技術演進與參賽者之爭

- 耗蝕性雷射釋放材料應用於RDL優先扇出 封裝優勢

# 23 設計實例

- 電源完整件還有新招?

- 使用分貝要謹慎

- 數位電位器模擬對數錐度以準確設置增益

- 一個雜亂無序的掃頻VCO電路板佈局

- 利用階躍激發進行穩定性測試

- 壓擺率和上升時間: 不盡相同

- 一種改進的新型閉鎖電源開關

- 採用低壓電晶體進行高壓電流檢測

# 39 新品櫥窗

• 內建AFE微控制器適用高精確度量測設備

#### 發行人

Yorbe Zhang

#### 副發行人

#### Grace Wu

grace.wu@aspencore.com

#### 內容查詢

台北: Judith Cheng

judith.cheng@aspencore.com

香港特別行政區: Yorbe Zhang

yorbe.zhang@aspencore.com

#### **Worldwide Sales Contacts**

#### China & Asia

Beijing Tel: +86-10-5913 3198 Hong Kong Tel: +852-2253 3972 Shanghai Tel: +86-21-5368 1223 Shenzhen Tel: +86-755-3324 8104

**Taipei & Singapore** Tel: +886-2-2759 1366 ext. 300 **Rest of Asia** Tel: +886-2-2759 1366 ext. 102

#### Americas

Tel: +1-510-757 3953 Tel: +1-803-236 2667

#### Europe

Tel: +49-8092-24774-11 Tel: +49-911-939764-42

#### **EDN-Taiwan**

(ISSN 2309-4311) is published monthly by eMedia Asia Ltd. All publishing rights and copyrights ©2019 are held by eMedia Asia Ltd. The magazine is distributed free to a limited number of qualified readers. Paid subscriptions are available for non-qualified readers. Please send subscription requests and change of addresses to emedia.support@ aspencore.com. Although every care will be taken, the Publisher accepts no responsibility for damage to or loss of photographs, transparencies, or other materials submitted for publication. Printed by C & C Offset Printing Co. Ltd, 1-9/F C&C Building, 36 Ting Lai Road, Tai Po, New Territories, Hong Kong.

**ASPENCORE**

# 人工智慧是否會進入 測試產業?

作者: Larry Desjardin, Modular Methods LCC總裁

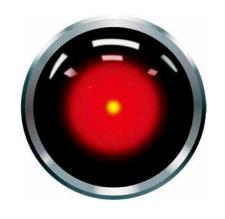

無論是名為人工智慧(AI)、機器學習(ML)還是專家系統,AI都已成為今天的新聞熱點。Elon Musk曾經警告說,快速採用AI存在潛在風險,而IBM則已在其Watson服務中部署AI,用來處理某些需要進行某種判斷的技術問題。科幻小說經常在情節中融入機器智慧元素,例如《終結者(Terminator)》系列電影中的天網(Skynet)、《2001太空漫遊(2001: A Space Odyssey)》中的HAL 9000(圖1),或者冷戰傑作《巨人:福賓計畫(Colossus: The Forbin Project)》。

暫且不提各種威脅情景,AI有可能在各種模棱兩可的情況下做出決策。這不僅僅是遵循自動流程圖,這些情況以往通常需要人來進行判斷。這就SI出了電子測試和測試工程話題,AI在這裡有用嗎?為了找到答案,筆者聯繫了許多公司,就他們的AI工作,以及如何看待未來進行了討論。

對於這個討論,我詢問了幾個具 體問題:

- AI是否真的適用?

- 今天是否有產品或服務使用了AI?

- 未來是否會有產品使用AI?

- 如果有的話,哪些應用最有希望?

- 你認為提供AI產品和服務有哪些 商業模式?

- 公司現在提供哪些AI產品和服務? 我的第一個有關AI適用性的問題缺少正面回覆。有幾家公司只是說他們沒有做AI方面的工作,或者至少他們覺得不方便說。所以,我們知道AI在測試領域不是主流,至少現在還不是。

從我收到的回覆中確實可以看到

一個重要的關聯性:半導體測試產業 似乎已在追求AI。

Teradyne最佳化設計(DfX)經理Mark Hutner和產品經理Yi Zhang一起進行了回答。他們看到AI在兩個方面具有應用前景:客戶生產經濟性和整體設備效率(以避免意外停機)。他們表示:「兩者都將透過提高良率和測試覆蓋、縮短產品上市時間和最佳化測試執行時間來為客戶創造價值。」他們看到,雖然今天是使用自我調整測試根目錄據規則進行測試最佳化,但是AI在此大有可為。「我們看到測試時間可縮短10~15%。」

在客戶生產經濟性方面, Teradyne認為,AI在觀察到初始故 障後,可進行良率恢復,從而增加價值。這樣可以實現更多測試,恢復不 太好的裸片。再結合基於AI的自我調 整測試,這就會對產品盈利能力產生 巨大影響。「良率恢復方法可使平均 測試時間得到最佳化,良率得到恢 復,借此,產品盈利能力可望提升超 過30%。」Hutner和Zhang表示。

由於每個客戶的基礎設施各不相同,Teradyne為多種離線資料分析工具提供資料通路。Optimal+是一家為半導體和電子公司提供端到端產品分析解決方案的公司,他們就提供這類工具,筆者採訪了該公司的技術院士Michael Schuldenfrei。

Schuldenfrei指出,Optimal+在 其用於半導體製造的若干軟體產品中 使用AI來彙集多組產地或參數故障特 徵相似的晶圓,進而辨識共同的根本 原因(圖2)。電子製造領域正使用神

圖1:《2001太空漫遊》中有一台AI電腦HAL 9000,它成為了「發現一號(Discovery One)」機組人員的敵人。AI變壞的假設例子不一而足,這就是其中之一。那麼,測試領域如果有一台這樣的新款HAL,它是否會告訴測試工程師說,「對不起,我不能那樣重新調整測試順序」?

(圖片來源:Pixabay)

經網路(NN)來分析各檢查步驟的輸出,借此提供更好的故障分類。「我們使用AI來找出PCB中的裂縫。」 Schuldenfrei表示。AI還可用來預測昂貴或破壞性工序(例如老化)的結果,以便可以跳過已預測通過的部分。

Schuldenfrei認為AI未來充滿希望。「隨著晶片、電路板和產品的複雜性不斷增加,製造、組裝和測試過程勢必產生大量資料。為了獲得相關的高價值的見識,AI就成為了處理這些資料的關鍵組成部分。

隨著電子產品在自動駕駛車等關鍵任務應用方面變得越來越普及,為了因應這方面的品質和可靠性要求,業界將加大對AI領域的投資,以便找出製造過程中潛在的不良元件,而防止用到它們。」

Optimal+透過年度訂購提供產

**圖2:AI可用來找出引起各產地晶圓良率問題的根本原因。**(圖片來源: Optimal+)

品。從長遠來看,Schuldenfrei預計 將會出現資料科學家把他們的AI模型 部署到Optimal+等提供的協力廠商平 台,而將它們變現的商業模式。這樣 的商業模式除了可以將AI部署到故障 分析、製造和測試最佳化以外,還可 以包含整個生命週期分析,他把它稱 為「聖杯(Holy Grail)」。

因此業界已有基於AI的產品。但 是半導體公司真的使用AI嗎?英特 爾(Intel)工程總監Rohit Mittal在向 EDN投稿的文章《Machne learning improves production test(機器學習 改進生產測試)》中談論了英特爾在機 器學習方面的應用。他表示:「本文 描述了一種方法,它可以在製造測試 期間,使用機器學習演算法,以及誤 差補償裕量,透過常規測量的參數可 靠地預測出難以測量的參數。然後, 這些預測值可用於在製造測試期間動 態設置其他影響良率的參數。這種 方法由於不依賴於早期設計驗證測試 (DVT)所得出的固定規範,還可以檢 測到由於元件或製程變化而產生的品 質漂移。」

從整體來看就很容易想到,為什麼半導體製造業可能最先採用機器學習進行測試。傳統的電子製造通常有賴於對已知良好的、預先測試的元件進行組裝,從理論上來講,如果設計正確,只有零件和製程缺陷才會導致故障。半導體製造卻不同——製程就是一切,包括「零件」的製造。實現高良率需要對多方面進行最佳化,而機器學習會是有用的工具。

那麼,傳統的電子製造業呢?這裡還有一段路要走。Bloomy Controls技術長Grant Gothing接受了筆者採訪,該公司在創建功能測試和資料擷取系統方面具有豐富歷史。

Gothing表示,Bloomy目前使用基於規則的演算法來最佳化生產功能測試系統(圖3)。他認為AI是未來的技術,可以協助對元件進行故障排除。這裡他強調的問題是語義:嚴格來說,基於規則的系統不算AI系統。然而,這類系統在實現許多相同結果方面非常有用。當技術人員排除故障,

打開複雜的電子元件時,它們可以為 其提供想法和建議。問題是,與基於 規則的系統或流程圖相比,AI系統還 有哪些優勢?

同時,這裡的關鍵問題是,AI增 強型產品是否會在功能測試方面找到 重要應用領域。從我自己的觀點來 看,這也是種財務權衡。畢竟,如 果良率變得夠高,是否還有令人信服 的理由,要把資源用於修復無用的元 件?或許有,但問題的答案非常取決 於環境。

那麼,回到「AI是否會進入測試產業」的問題,我認為這對於半導體產業來說是肯定的,業界已經有產品和成熟的答案。對於研發或製造領域方面的傳統電子測試系統,答案尚不清楚。但有件事可以肯定,那就是所有這些工具都是用來幫助工程師,而不是取代他們。工程師不用擔心機器會搶了他們的工作,至少現在還不會。

圖3:雖然半導體測試看起來已準備好開發AI,但電子功能測試的前景並不確定。 (圖片來源: Bloomy Controls)

# 分析主流SiC MOSFET和 GaN HEMT元件

作者:胡安,EDN China

據Yole Développement預測,到2023 年,SiC功率半導體市場預計將達到15 億美元。基於SiC的功率半導體用於 600V~10kV應用,大多數SiC應用集 中在600V~1,700V。

商用的SiC半導體元件有SiC蕭特基二極體、SiCJFET及SiCMOSFET。自2011年,Cree推出第一代SiCMOSFET,數家半導體公司已經量產SiCMOSFET。市場上主流的SiC產品如表1。

在一次技術論壇上,中國清華大學電機工程與應用電子技術系教授許烈比對了幾款主流SiC MOSFET與Si MOSFET的性能,如表2所示。

從表2中可以看到,SiC MOSFET 相比Si MOSFET的明顯優勢包括: 更小的導通電阻、更快的開關過程、 更小的寄生電容、更高的工作溫度、 更好的三極體反向恢復特性。缺點包 括更高的反向三極體導通壓降、驅動 電路更複雜、系統對於雜散參數更加 敏感。

另外,SiC MOSFET相比Si IGBT的明顯優勢包括:無拖尾電流現象、

| 耐壓等級 T。=25℃           |

|-----------------------|

| 900V/1000V/1200/1700V |

| 650V/1200V/1700V      |

| 1200V/1700V           |

| 650V/1200V            |

| 1200V                 |

| 1200V                 |

|                       |

表1:主流SiC MOSFET產品。

|                  |                     | Si MOSFET<br>(IXYS) | Si CoolMOS<br>(Infineon) | SiC MOSFET (Wolfspeed) | SiC MOSFET<br>(Rohm) |

|------------------|---------------------|---------------------|--------------------------|------------------------|----------------------|

| 元件型號             |                     | IXFN32N120P         | IPW90R120C3              | CPM2-1200-<br>0025B    | SCT3022KL            |

| 電壓等級/V           |                     | 1200                | 900                      | 1200                   | 1200                 |

| 電流等級/A<br>Tួ=25℃ |                     | 32                  | 36                       | 98                     | 95                   |

| 導通電阻/<br>mΩ      |                     | 310                 | 120                      | 25                     | 22                   |

| 開關瞬態時<br>間/ns    | t <sub>d(on)</sub>  | 70                  | 70                       | 14                     | 29                   |

|                  | t,                  | 62                  | 20                       | 32                     | 44                   |

|                  | t <sub>d(off)</sub> | 88                  | 400                      | 29                     | 67                   |

|                  | t,                  | 58                  | 25                       | 28                     | 28                   |

| 寄生電容/            | C <sub>iss</sub>    | 21000               | 6800                     | 2788                   | 2879                 |

| 可土电台/<br>pF      | $C_{oss}$           | 1100                | 330                      | 220                    | 237                  |

| ρг               | C <sub>rss</sub>    | 77                  |                          | 15                     | 108                  |

|                  | 正向壓降/V              | 1.5                 | 0.8                      | 4.0                    | 3.2                  |

| 反向二極體<br>特性      | 反向恢復<br>時間/ns       | 300                 | 920                      | 45                     | 28                   |

|                  | 反向恢復<br>電荷/nC       | 1900                | 30000                    | 406                    | 175                  |

表2:SiC MOSFET與Si MOSFET的性能對比。(資料來源:許烈)

更快的開關過程、更小的寄生電容、 更高的工作溫度、關斷時間對負載電 流和溫度不敏感。缺點是驅動電路複 雜、系統對於雜散參數更加敏感。

許烈指出:「SiC元件的反向恢復電流很小,而且負載電流變化時其變化不大。而Si二極體的反向恢復需要電子和空穴的複合,使其反向恢復時間長,反向恢復電流大,同時也受負載電流影響。」

GaN用於15~600V的應用,主流產品如表3所示。

許烈表示,寬能隙半導體元件在設計中的關鍵問題包括:門極電壓允許範圍比Si基元件更窄;開關速度更快,帶來EMI問題;更高的雜散參數、保護回應速度、驅動電路設計要求。

另外,現有SiC封裝仍使用Si元件 封裝技術,限制了SiC元件的使用溫 度,這也是未來需要改進的一個方向。 同時,許烈表示,高溫也是個系統問題,需要從高溫功率元件、控制晶片、 電感、電容、線纜等多角度解決。

| 增強型GaN HEMT      |             |           |  |  |  |

|------------------|-------------|-----------|--|--|--|

| 廠商               | 門級結構        | 耐壓等級      |  |  |  |

| EPC              | P-GaN Layer | 15V~200V  |  |  |  |

| GaN System       | Insulated   | 100V/650V |  |  |  |

| TI               | Insulated   | 80V       |  |  |  |

| Panasonic        | P-GaN Layer | 600V      |  |  |  |

| Infineon         | P-GaN Layer | 100V/600V |  |  |  |

| Cascode型GaN HEMT |             |           |  |  |  |

| Transphorm       | Cascode     | 600V/650V |  |  |  |

| Infineon         | Cascode     | 100V/600V |  |  |  |

|                  |             |           |  |  |  |

# NIWeek 2019現場直擊

作者: 啟明, EDN China

我們現在生活在偉大的技術加速時代。感測已無處不在,世界上部署的感測器正在接近1兆個;連接設備也在接近300億台;機器學習也已不再只是個流行名詞,而是已應用到許多領域。這些所有加在一起,使我們面臨前所未有的巨大挑戰,這對大家意味著什麼?也就是每個人都在參與5G、自動駕駛車、工業4.0或商業太空旅行的競賽。這是NIWeek 2019大會的開場白,也預示了此次活動的重點。

這個會議訊息量巨大,本文節選幾個重要創新以饗讀者。

# Qorvo:5G手機有60%以上重大RF更改

Qorvo 5G業務開發總監Ben Thomas受邀探討了5G技術的現狀及其對業務的影響。Thoma指出,5G的第一階段,3GPP Release 15於2018年底批准;預計第二階段將在2020年作為Release 16的一部分批准,所有這些都旨在儘快將5G放到消費者手中。

他並表示,部署5G技術的最大挑戰是其更加複雜,5G 引入了新的頻段,其中大部分頻寬比LTE寬得多。5G還增加 了許多載波聚合組合、雙上行鏈路,以及更複雜的波形和調 變方案。

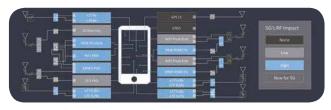

要瞭解5G的複雜度,只需看看5G手機的系統圖(**圖1**)。將手機發展到5G需要對60%以上的RF內容進行重大更改——包括多個新的5G RF元件。

Qorvo在10多年前就開始使用NI的PXI和軟體進行自動驗證測試。使用這一平台的動機是什麼?Thomas指出,產業從3G轉向4G,RF設備的測試複雜性開始爆發,使用傳統儀器進行RF測量非常耗時,且考慮到測試用例的數量,所需測試平台的數量可能加倍甚至增加到三倍,而採用PXI則能夠在不犧牲測量品質的情況下顯著提高測試輸送量。

此外,他指出,Qorvo正在大規模生產世界上第一款專為新型n77 5G頻段設計的RF前端模組。這款RF前端將PA、LNA、濾波器和開關整合在緊凑的封裝中——在當今市場上的一些領先的5G智慧型手機中就會用到它。

圖1:5G手機系統圖。

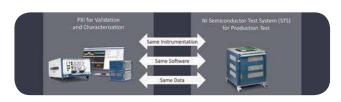

圖2:NI生產測試用STS源自實驗室測量。

# 毫米波VST、STS、5G毫米波半導體探針測試解決方案三管齊下

NIWeek大會上,NI發佈了毫米波向量訊號收發器(VST)。 與之前的VST類似,該儀器將RF訊號產生器和RF訊號分析 儀組合到一台儀器上,該儀器擴展了其產品組合,不僅可 以處理5G sub-6GHz頻段,還可以處理5G毫米波頻譜。

NI半導體測試系統解決方案經理Anita Salmon表示,現有的毫米波測試產品速度太慢,功能設置不完整,並且測試環境整合非常麻煩。因此NI將生產測試測量速度與實驗室級測量性能相結合,推出了半導體測試系統(STS),如圖2所示。

此外,毫米波晶片的設計與6GHz以下產品有很大不同,製造充滿風險。降低風險需要的不只是一個產品,而是要有高度整合的解決方案。因此,NI與Tokyo Electron、FormFactor和Reid-Ashman合作開發了5G毫米波半導體探針測試解決方案。

### 攝影鏡頭影像拼合:消除駕駛常見盲點

Valeo測試開發經理Chris Forristal介紹了如何使用NI平台加速汽車安全系統的發展。

目前駕駛面臨的一個挑戰是駕駛掛有拖車的卡車。這可能給駕駛帶來新的困難,無論是在造成視野模糊、增加駕駛複雜性方面,還是向前、向後駕駛等方面。為了幫助駕駛,Valeo想了一個點子,將連接到拖車後部的攝影鏡頭與卡車上的攝影鏡頭之間的影像合併。稱為XtraVUE拖車系統(圖3),在今年的消費電子展(CES)上已經推出。

「我們在拖車後部安裝了一個小型攝影鏡頭,只需將拖車後面的影像縫合到汽車的後視攝影鏡頭即可。司機現在不僅可以看到全景,還可以看到拖車後面。這消除了駕駛的常見盲點。」Forristal介紹,「不僅每輛拖車各不相同,而且還有其他考慮因素,例如卡車轉彎時拖車的旋轉,以及卡車攝影鏡頭和拖車攝影鏡頭之間的實際間距。Valeo的專利技術可以在6個軸(每個攝影鏡頭有×、y、z三個軸+旋轉)上進行校準。

# 技術脈動

圖3:XtraVUE拖車系統演示。

因此用戶無論將攝影鏡頭安裝在拖車的什麼位置,都可以將看 到的影像調到居中。」

其中用到了NI的PXI平台進行標準化。該平台用於新技術的開發與驗證,既提供了經驗證的現成技術的最佳組合,又讓客戶可以靈活地使用自己的軟體進行定制。FlexRIO在這些設置中扮演著重要角色,其上的開放可程式設計FPGA能夠克服所面臨的幾個最複雜的挑戰。「我們使用FlexRIO作為主攝影鏡頭介面,從而可以初始化、即時控制和擷取攝影鏡頭的資料。」他指出,「這些資料可提供大量價值。我們用它來訓練和驗證視覺演算法,在演算法開發期間在軟體環境中重新處理資料,並在驗證實驗室裡在工作台上的ECU硬體上進行重播。我們甚至開始使用PXI生成合成資料,以協助在實驗台上的閱環HIL環境中測試拖車檢測等內容。」

「從設計驗證到環境測試和生產,我們在所有測試領域使用相同的PXI和FlexRIO系統。與硬體平台模組化一樣,我們的軟體平台也是如此。我們建立了一支強大的LabVIEW開發團隊,並圍繞內部開發的外掛程式架構進行了標準化。」他補充,「我們需要做的就是重新設計FlexRIO的攝影鏡頭介面,其他90%的硬體和軟體可以直接重複使用。」這個系統也獲得了Edmunds頒發的年度CES技術驅動創新獎。

# 虛擬工廠:實現超過2,000萬美元收益

Deloitte物聯網(IoT)技術專家Robert Schmid展示了「Deloitte虛擬工廠」應用。並演示該公司交鑰匙物聯網解決方案如何將NI平台與CompactRIO和InsightCM結合,將資料傳遞給邊緣以找到隱藏的價值,並創建未來的智慧工廠。

透過平板電腦可以看到基於某客戶真實工廠生產線的擴增 實境(AR)重現。據說,該客戶利用這個方案實現了超過2,000 萬美元收益,整體設備效率提高9%。

圖4:小型衛星透過「宇宙女孩」波音747從高空發射。

這個平台中的元素,如CompactRIO、InsightCM、無線節點和LabVIEW,在將測量和物聯網引入製造的過程中發揮著關鍵作用。「無論是進行手機或風力渦輪機的離散製造,還是聚合物或石油的加工製造,它都適用。」Schmid表示。

# 小型衛星高空發射也可以很便宜

Leonardo旗下的Selex設計了一種創新的被動雷達系統; SAAB航空徹底改變了Grippen戰鬥機的硬體在環驗證系統;Honeywell International航空航太對生產測試的硬體、軟體和流程進行了標準化。那麼,現在還有比新太空產業更酷的東西嗎?

Virgin Orbit這家公司提供了專用小型衛星發射服務,為小型衛星發射革命開創了空間。傳統衛星的重量是數千公斤,建造和運作需要數億美元,而且需要借助相當大而昂貴的火箭才能進入太空。重達幾百公斤或以下的小型衛星馬上就被視為「二等公民」,但是它們具有構建快速且成本低,以及規劃和技術更新週期短的真正優勢。因此必須考慮新方法,將這些衛星送到太空去。

Virgin Orbit設計了一種與客戶能力相匹配的發佈系統。它使用名為「宇宙女孩」的波音747將火箭運送到大約35,000英呎的高度,然後將其釋放並發射到軌道。也就是說,火箭可以從世界上幾乎任何地方發射並靈活地進入任何軌道,在高空發射可以使所用燃料明顯減少,能夠在不犧牲品質的情況下提供價格合理的太空發射。

但是,像火箭這樣高風險的任務必須進行全面測試。747 火箭發射的大部分測試都基於NI的平台,以滿足極其激進 的計畫所需。從多級航空電子硬體在環測試台,到飛行 驗收和鑒定測試、發射控制,以及飛機上的火箭和有效 載荷狀態監控,該公司使用包括LabVIEW、VeriStand、 TestStand、SystemLink、PXI、CompactRIO和 CompactDAQ等各種NI的軟硬體平台,目標是確保在飛行之 前能盡可能多地測試和重新測試各種可能情況。

### 什麼是認知雷達?

美國賓州州立大學(Pennsylvania State University)博士 Ram Narayanan和陸軍研究實驗室的Brian Phelan,以及 NI產品行銷經理Leah Langston共同探討了正在合作的開 創性雷達技術——認知雷達。

Narayanan介紹,認知這個詞與感知、記憶和推理有關,這些都是人類自然而然在做的事。從根本上說,雷達是一種利用無線電波探測其環境的探測系統,傳統上會有一個雷達操作員手動改變操作以在不同方向上實現探測,或者如果訊號受到干擾,就可能需要調整工作頻率。認知雷達的目的就

是將其思維和經驗帶入硬體中,以便使這些決策可以自動發生,並優於最佳操作員。

有很多應用都可以從認知雷達中受益,例如直升機著陸 援助及空中和導彈防禦。

設計認知雷達系統的最大挑戰是感知環境的時間需要極短,並相應地更新雷達的指令引數。通常,這些調整必須在百萬分之一甚至十億分之一秒的數量級上進行,這很難做到,而如果使用FPGA在硬體中實現演算法,則可以滿足這些時序要求。但是要成為傳統FPGA設計語言(如VHDL或Verilog)的專家可能需要數年時間。相反,LabVIEW則可以讓他們專注於實際頻譜感知和認知雷達方面的設計,而無需成為FPGA專家。

# 讓超音波成為第三個醫學史上創新

還有一個很厲害的案例使用了NI的PXI和STS。Butterfly Network測試工程經理Andrew Betts指出,世界上有60%的人無法獲得任何現代醫學影像,如超音波。即使在發達國家,價格和缺乏專業知識也可能致使人們無法利用超音波來進行診斷。在醫學史上,只有兩項創新產生了真正的全球影響:疫苗接種和抗生素,Butterfly Network的使命是讓超音波成為第三個。

該公司團隊利用半導體技術代替傳統的壓電晶體將多個超音波探頭組合成一個寬頻頻率設備,並使用已建立的半導體供應鏈將價格降至消費電子水準。Butterfly-on-a-Chip晶片是Butterfly iQ設備的核心。這是世界上第一個FDA批准的全身探測器,售價不到2,000美元。

急診需要快速。「我可以將探針插入iPhone或iPad。啟動應用程式,選擇探頭預設,然後將它貼在我的脖子上查看頸動脈。打開彩色都卜勒(編按:亦即彩色超音波),就可以顯示血液經由動脈流到大腦。」Betts說。

但是,將片上超音波等新技術推向市場必然會遇到一些 挑戰,例如如何平衡測試開發的複雜性和更快上市時間的業 務需求。

「我們將工作流程劃分為內部測試儀的硬體和軟體發展,同時將製造操作和測試執行任務外包給OSAT。」他指出,「之所以能在內部採用STS開發,是因為其靈活並且可訪問。我們需要可定制的測試解決方案,其軟體開放,可以支援C#和Python。STS提供了I/O定制和資源密度,具有極具吸引力的成本目標和緊湊的佔位面積,因此我們可以在康乃狄克州(State of Connecticut)實驗室進行開發。透過轉換到STS在內部進行開發,反覆運算時間可從三周縮短到一天。」

今年初,Butterfly Network的成果在奧斯丁獲得SXSW的健康、醫療和生物技術創新獎,以及最佳展示獎。

# 矽光子步入黃金時代

# 封面故事

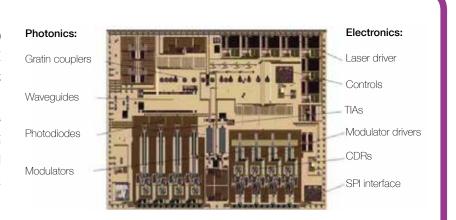

矽光子一直是一項極具吸引力的技術。既然對光通訊中所用紅外線波段的光子來說,矽是透明的,那麼為什麼不將光學元件整合到矽片上呢?絕緣矽(SOI)製程可用於在矽中形成波導、調變器和其他光學結構,並充分利用CMOS的低成本與可擴展性。

經過數十年的研發,矽光子產品在過去幾年中已經進入市場並進入實際應用(圖1)。該技術在資料中心尤其具有吸引力,因為超大規模設施上線需要數百公尺的中心內鏈路,而它們最好的解決方案是光纖。目前,這當中使用的是可插拔收發器模組,但是如果將收發器整合到與電子元件相同的封裝中,則將更具成本、空間和功耗方面的優勢。

傳統的光學元件通常需要手工組裝成氣密、離散封裝的元件。將一些光學元件整合到砂上可以充分利用電子封裝的成本優勢和組裝的便利性, 而且,矽光子還可以實現超大規模資料中心所需的容量增長。

實際上很多營運商在4G擴建時已經開始在行動前傳(mobile fronthaul),特別是在天線上的天線與基頻單元之間的鏈路中採用光纖來加速安裝。而5G的出現,對速度和頻寬有了更高要求,這也為矽光子創造了另一個機會。

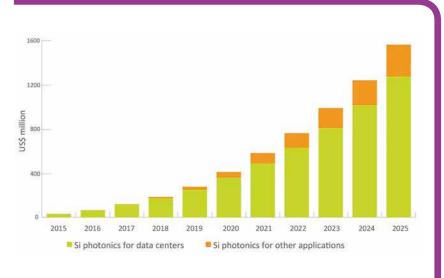

Yole Développement估計2018年 矽光子的全球市場價值將達5億美元,

**圖1:2016~2025矽光子市場預測。**(資料來源: Yole Développement)

而到2025年將增長至35億美元。這 其中包括了一些潛在應用,如資料中 心、5G、光達(LiDAR)和生物感測器。

「儘管出現了很多新創公司,但這仍然是一個非常集中的市場,由英特爾(Intel)和思科(Cisco)最近收購的Luxtera所主導。」Yole Développement光子、感測和顯示器分析師Eric Mounier表示,「矽光子的總資金數可能接近10億美元。其原因是它極有希望解決資料中心的頻寬瓶頸問題,同時它也是感測器應用的一個優秀技術平台。」

一些大公司已經在這方面投入了 鉅資。例如,英特爾在過去幾十年 裡一直在研發矽光子技術,還有一 些公司則透過收購進入該市場。思科於2019年2月以6.6億美元的價格完成了對Luxtera的收購。出人意料的是,2019年3月Nvidia也宣佈計畫以69億美元的價格收購光纖互連領軍者Mellanox,此次交易將為Nvidia帶來矽光子產品組合,這又基於Mellanox在2013年收購Kotura時所獲得的技術。在此之前,Nvidia已經透過其圖形處理器產品在資料中心領域佔據了很大席位——資料中心市場約佔其業務的25%,Nvidia-Mellanox陣容將使資料處理和互連構成同一解決方案的組成部分。

「Mellanox的主要競爭對手是英特爾,英特爾正在資料中心互連方面推動矽光子技術取代矽技術。」Yole Développement總裁兼執行長Jean-Christophe Eloy表示,「英特爾希望為其已經在賣給資料中心製造商的資料處理添加光互連。而隨著對Mellanox的潛在收購,Nvidia也正在採取同樣的策略…對於Nvidia而言,這是一個聰明的做法,但這對英特爾來說就是個壞消息了,因為他們將面對一個創新且發展迅速的競爭對手。」

英特爾於2016年宣佈其首款矽光 子元件的量產,此後又增加了兩款產

圖2: 英特爾的矽光子100G CWDM4 QSFP28光收發器,支援擴展溫度範圍工作。 (圖片來源:英特爾)

# 封面故事

品。這三款元件分別是用於資料中心應用的100G和400G收發器,以及針對5G前傳的具有擴展工作溫度範圍的100G收發器。這款用於5G的產品是一款CWDM4 QSFP28稀疏分波複用(CWDM)、四通道小型可插拔收發器,支援在-40℃~85℃的工作溫度範圍內透過單模光纖實現10km鏈路(圖2)。

Mounier表示,由於矽光子技術 具有優於傳統光學技術的先天優勢, GAFAM科技五霸權——Google、 蘋果(Apple)、Facebook、亞馬遜 (Amazon)和微軟(Microsoft),以及 BAT中國網際網路三巨頭——百度、 阿里巴巴和騰訊等公司,正在積極推 動這項技術的發展。同時,晶圓代工 廠也致力於為無晶圓廠矽光子客戶提 供通用製程。

「確實有越來越多的代工廠對矽光子感興趣,無論是意法半導體(STMicroelectronics)、GlobalFoundries和台積電(TSMC)這類大型晶圓代工廠,還是各種微機電系統(MEMS)代工廠,如SilexMicrosystems、APM和VTT,」Mounier表示,「GlobalFoundries已經與許多矽光子無晶圓廠建立了廣泛的合作關係…透過利用GlobalFoundries現有的半導體製造平台,矽光子將會帶來更多業務。」

# 雷射對準

通訊巨擘MACOM是其中一家與GlobalFoundries合作擴展其砂光子技術的公司。這兩個合作夥伴在2019年3月簽署了一項協定,使MACOM可以在GlobalFoundries工廠中使用其自對準端面蝕刻面技術(SAEFT)。

由於雷射無法用砂製造(它需要用磷化銦等直接能隙材料),因此通常是採用倒裝晶片組裝製程將單獨的雷射裸片組裝到砂光子晶片上並精確對準。MACOM專有的SAEFT自對準製

程可實現雷射裸片與砂光子晶片(PIC) 對準,從而製作L-PIC。該技術基於 EFT技術,是MACOM於2014年收購 雷射供應商BinOptics所獲得。

「這種自動化自對準製程取消了雷射的主動對準,以及離散光學設計中傳統環氧樹脂固定與固化步驟。」MACOM矽光子產品行銷總監ArlenMartin表示,「與GlobalFoundries達成的協議是雙方現有關係的延伸,並使新加坡和紐約的多源供應鏈能夠利用GlobalFoundries的製造。MACOM將充分利用GlobalFoundries的300mm(12时)矽製造製程來達到急需的規模與成本要求。」

根據Martin所述,MACOM正在 為資料中心和電信客戶開發基於其 L-PIC平台的新產品,包括提供100G CWDM4、100G DR1/FR1、200G FR4、 400G FR4和400G DR4解決方案,以 便實現向100Gbps、400Gbps,以及 更高傳輸速率過渡。

砂光子非常適合5G電信網路等高容量應用。他表示,「5G前傳部署的第一階段將是10G SFP+和25G SFP28模組的混合部署。對於中傳,光學部分將過渡到Nx56G四階脈衝振幅調變(PAM4)QSFP模組。在我們從10和25Gbps過渡到50和100Gbps的過程中,預期砂光子將開始發揮重要作用。」

# 矽鍺(SiGe)

Sicoya是從柏林工業大學(Technischen Universität Berlin)拆分出來的一家公司,憑藉其研發的、基於矽鍺BiCMOS

**圖3: Sicoya的單片整合式100G光電IC。**(圖片來源: Sicoya)

圖4: Sicoya的單晶片100G QSFP28收發器。(圖片來源: Sicoya)

# 業界首選的工業乙太網路產品

fido5000 讓支援用於智慧工廠的多協定可更簡易地併入單一工業乙太網路介面。 為將來做好準備, fido5000 提供了一條 通達 TSN (時間敏感網路) 的清晰路徑, 隨著協定在智慧、互聯的工業 4.0 大環境 下不斷進化,實現因應未來的應用。

# fido5000 協助確定性 乙太網路設計

# 封面故事

製程的100G矽光子收發器於2017年進入市場。大多數矽光子公司都採用SOI 製程構建其元件,但Sicoya執行長Sven Otte卻稱「從BiCMOS電子元件著手並添加光子才是天作之合。」

「這是有道理的,因為大多數光學互連的電子部分不管怎樣都要採用BiCMOS,」Otte表示,「跨阻抗放大器、時脈和資料恢復,以及雷射驅動器都是採用矽鍺BiCMOS…CMOS則僅用於需要訊號處理的地方。」

如今,Otte表示,「Sicoya的電子和光子已整合在同一個晶片上,這使得我們的電晶體比CMOS電晶體速度更快。矽鍺是一種超高效的技術,它不僅在性能上為我們帶來優勢,同時還取消了某些封裝工序。」

即使可能的話,在矽片中有效構建雷射二極體和光電探測器(PIN二極體)等光學元件也非常困難,因此大多數矽光子解決方案是將這些元件放在單獨的裸片上。而Sicoya將矽鍺光電探測器整合在與接收側電子元件相同的裸片上(圖3)。該公司是否會嘗試構建矽鍺雷射,來實現更加整合的發送端呢?

「我們可以做到,但對於所需的特定波長,它還不夠好。」Otte表示,「更有可能的是,在我們的一款晶片上面生成一層磷化銦層來形成雷射。但這仍處於研究階段,完成原型和資格認證也還需要一些時間。」

Sicoya擁有混合商業模式,它向策略性大容量客戶同時銷售晶片和引擎。「我們還將使用這些晶片的光收發器賣給那些Web-scale公司。它們只接受光收發器——通常,他們不接受任何光引擎——而且我們發現向收發器公司推銷產品是一件很困難的事情,因為我們是在與其內部技術競爭。」Otte說。

Sicoya產品包括2017年推出的 100G收發器系列和2019年3月在

圖5: Rockley Photonics在OFC2018上 展示了其Topanga 12埠100G乙太網路交 換機 ○ (圖片來源: Rockley Photonics)

OFC2019展會上首次推出的三款400G收發器系列(圖4)。400G型號目前正在進行資格認證,並將於今年下半年開始出貨。此外,還有一款針對5G基礎設施設計的產品——28G單通道單模收發器——並正在開發其CWDM版本。

「網路架構已經發生變化,從天線和遠端基地台之間的銅纜連接,再到都會區網路的光纖連接,以及現在的射頻前端,其將天線直接連接到光纖收發器…資料傳輸速率高很多。」Otte談道,「這些連接大多是點對點、單通道。在大都市區,有時一座天線桿上會有多根天線,在這種情況下,就需要用CWDM收發器,才能僅用一根光纖連到遠端基地台。

Otte還強調了矽光子對於5G基礎設施的幾點優勢。矽光子晶片本質上對溫度不敏感,因此它們可以承受5G部署中經常遇到的從狂風暴雪到沙漠酷暑的極端環境條件。這項技術還易於擴展,設計不會過時,對於5G來說,這是一個明顯優勢。另外還有成本優勢,傳統的離散式解決方案,封裝佔了成本的很大一部分;而貼裝了雷射裸片的矽光子晶片可以採用電子封裝,相比之下,只需最少的製程步驟。

Otte很清楚5G基礎設施不是未來的應用,而是正在發生的應用。「我們正在5G市場加速推廣我們的產品;今年年底之前,我們一家中國的電信

客戶就會把它安裝到現場。」他說, 「5G是我們在市場上看到的最大數量 的驅動力之一…對我們來說,5G市場 的規模比資料中心市場要大2~3倍。」

除了在柏林擁有工廠, Sicoya剛剛宣佈計畫在中國天津開設光模組和光引擎裝配和測試工廠。新工廠將服務於中國市場的5G無線前傳和100G/400G資料中心收發器應用。

「中國在部署5G方面特別領先,但在矽光子技術領域並不一定處於領先地位。」Otte談道,「事實上,我認為歐洲和美國在矽光子技術方面比中國領先2~3年的時間,這對我們來說是一個巨大的機會。」

### 未來

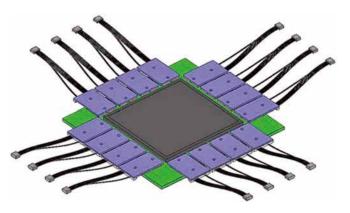

儘管矽光子技術未來的發展前途非常誘人,但物理上卻可能存在限制。 Rockley Photonics執行長Andrew Rickman認為,未來的光連接應該是 封裝內光學——將最佳化的矽光子與 微電子裸片整合在相同的封裝內,而 不是在相同的裸片上。

「光子和電子的特性差異巨大,」 Rickman說,「因此,開發最佳化電子IC所需的製程與開發最佳化光子IC所需的製程將會不同。這就是為什麼單片整合——雖然這個想法很誘人——永遠無法實現矽光子的全部潛力。現在我們在封裝技術方面已經有了重大創新,例如2.5D和3D晶圓級封裝,可用於開發和製造最有效的整體解決方案,可以預見這種方案將持續一段時間。」

Rickman指出,雷射需要採用直接能隙(III-V)材料實現,因此所有矽光子解決方案都至少需要多個裸片。關鍵在於將解決方案正確劃分到不同的裸片上,而不是進一步的整合,他表示。

「我們相信,最佳解決方案最終會 是將數位內容和類比前端(AFE)進行單

圖7:使用Rockley Photonics的矽光子平台進行資料通訊 的收發光學元件。(圖片來源:Rockley Photonics)

片整合,而矽光子和雷射仍然保持各自的製程——這就是我們用Topanga (該公司在OFC2018上的展示設備)演 示過的方法。」Rickman表示。

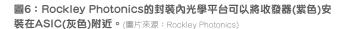

Topanga是一款12埠100G乙太網路交換機,預裝了全部12個100G收發器(圖5)。它採用的1.2Tbps乙太網路交換機ASIC是該公司自主設計,具有第三層路由功能,以及多個類比前端,用於所有48×25Gbps電通道。ASIC與矽光子IC封裝在一起,實現基於平行單模光纖的光介面。光功率採用外部雷射模組來提供,將PIC直接安裝在CMOS裸片附近,可最大限度地縮短高速電通道的長度,從而簡化設計並降低功耗(圖6)。

Rickman表示,在Rockley的封裝內光學想法流行起來之前,有種可能的中間解決方案是對類比前端和矽光子PIC採用單獨的裸片,將它們組裝到同一個封裝中,同時提供標準的電氣介面,來實現與協力廠商交換機晶片的互通。Rockley用其LightDriver產品推行這種方案,用於為包括資料中心連接、消費類感測器和光達在內的多個領域提供交換機相容(switchagnostic)平台。該公司在OFC2019上展示了使用該平台的收發光學元件(TROSA),如圖7所示。未來構建在

這個平台上的系統可能會在系統級上 再做最佳化——可能其數位ASIC的整 合度將會更高,或者會對電氣互連進 行最佳化,Rickman表示。

Rickman還指出,由於光的特性,矽光子與高階CMOS節點並不相容,因此與整合化的宣傳相悖。「大多數製造矽光子晶片組的公司都來自傳統的微電子產業,它們使用過去但尚未得到驗證的策略來利用現有的矽CMOS晶圓代工廠和製程。」他談道,「問題在於光子和電子的性能有很大不同,因此,針對電子而最佳化的CMOS節點不一定能成為光子光路高度最佳化的最佳選擇。」

因此有幾個實際考慮因素。矽光子需要採用SOI CMOS製程,其尚未達到與標準CMOS相同的先進節點,而且標準的製程流程尚未實現某些所需的特定工序。此外,要想用矽片製作高速調變器,波導必須縮小到亞微米尺寸,這遠小於其所通過的光波長。在這樣的微小尺寸下,傳播損耗將會增加,效率會降低。

「重要的是要記住,光子元件比電 晶體還要大。」Rickman表示,「把7 奈米(nm)裸片上寶貴的空間都用來實 現光子光路,那麼晶片上所剩下可用 來實現高速數位內容的空間就少之又 少,我們認為這種方法在經濟上行不 通。雖然Rockley的平台完全能夠生 產標準CMOS衍生製程流程中所有的 可能功能元件,但它的一個優勢是能 夠為光子最佳化解決方案提供所有元 件、設計功能和材料系統。」

Rockley於2017年與中國光纖電纜 製造商江蘇亨通光電成立合資企業,使 其技術實現了商業化。

亨通投資4,200萬美元建立這家合 資公司,目的是為市場提供低功耗、 高性價比的收發器。亨通今年初按照 交易計畫,又對Rockley的E輪融資投 資3,000萬美元。

「這家合資公司目前在提供100G市場所用產品方面進展順利,這將有助於推動中國電信和資料中心市場方面的業務。」Rickman表示,「最近我們宣佈了擴大我們的合作關係,這樣這家合資公司也能夠採用Rockley的LightDriver技術構建400G DR4收發器。這類產品將於年底開始發貨,借此我們將會擴大我們在中國乃至世界其他地區的影響力。」

經過數十年的研發,矽光子正在全球各地的晶圓廠中上量,資料中心的連接和前傳也將借此實現重大改進。或者,正如Otte所說,「矽光子已步入黃金時代。」

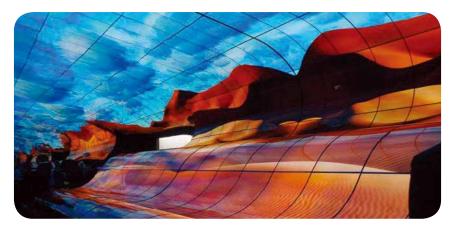

# 解析顯示技術演進與 參賽者之爭

作者:Brian Dipert,EDN資深部落客

上一次筆者詳細介紹大尺寸顯示器技術時,LCD液晶顯示器才開始取代傳統CRT、等離子和採用投影技術的設備而逐漸佔主導地位。當時OLED也已經興起,卻因一些技術上的不足而受到限制,多用於可穿戴設備、智慧型手機和其他小型和(或)「一次性」電子設備中。

接下來的十年,從某種意義上來說技術的發展完全可以預見。螢幕越做越大,畫素密度(即給定螢幕尺寸的解析度)也越做越高,LCD仍是主流。傳統的色彩平衡發生了變化(特別是藍色光譜),隨著技術的發展,強環境光下的可見性及其他歷史遺留問題逐步得到解決,樂金(LG)繼續努力推進OLED進入電視、零售展示和其他大螢幕應用。

但是正如我在今年消費電子展(CES)的報導中所指出,LG在OLED產品上的老競爭對手三星(Samsung)似乎正將其大螢幕的開發重新定位於QLED和Micro LED這兩種替代技術,這有些令人驚訝。這兩種技術雖然聽起來很像,實際上卻完全不同。瞭解這兩種技術和相對於LCD和OLED的一些實現細節,以及三星想用高利潤率的專利技術賭一把的打算,就明白為什麼要採用這兩種技術了。以下分析當前顯示技術市場的領導者與後進者的王位之爭。

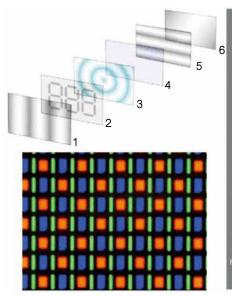

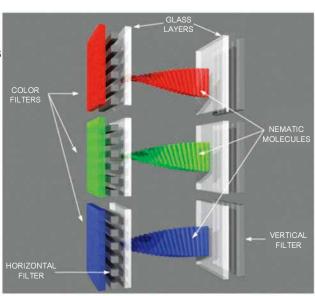

### LCD

LCD技術的基本優勢在於它長壽,或者說在於它成熟,因為它已經蓬勃發展了幾十年(也可以說超過一個世紀,

看從什麼時候開始計算)。我從2010 年的文章中拷貝了幾張圖和一些文字 來簡單回顧一下LCD技術。

通常,兩個平行偏振片的偏振方向垂直,這阻擋了光的傳輸,從而產生可感知的黑色畫素陣列。但氧化銦錫(ITO)可提供夠強的電場來改變中間液晶的調變特性,並轉化為不同強度的透光率。

主動矩陣LCD使用薄膜電晶體(TFT)矩陣技術,每個畫素至少分配一個電晶體,以實現精確的列線到畫素的相關性。顯示控制器啟動行線之後,將驅動列線上相關畫素的電壓。利用目前使用較多的扭曲向列型(TN)LCD,隨著所施加的電壓不斷變化,液晶元件發生不同程度的扭曲,與偏光鏡相互作用後可通過不同量的光。

圖1:傳統的LCD畫素結構很容易理解,但是這種結構發生極小的變化都會使結果產生很大的差異。向眼睛提供色彩最常見的方法是RGB子畫素三元組,也有許多其他方法,例如左圖中的PenTile排列。

精確的電場控制與刷新模式調變技術相結合,可以生成任意值的每畫素灰度。平面轉換(IPS)LCD的出現滿足了顯示器使用者對改善視角、更深的黑色及其他增強功能的要求。IPS LCD電平對齊液晶單元,並透過晶體端部對每個畫素施加電場,每畫素需要兩個電晶體,這使得IPS技術比TN技術更加昂貴。

不斷變化的扭曲和刷新調變技術使LCD能夠動態校準每個畫素的亮度,從而在範圍極值之間產生純黑、純白和灰色陰影。子畫素是LCD從白色背光源中產生顏色的關鍵。例如,傳統視訊圖形陣列(VGA)解析度面板307,200個畫素中的每一個都包含三個近距離子畫素,每個子畫素具有相關聯的紅色、藍色或綠色濾光鏡,只有可見光譜部分才能通過。對子畫素的選擇性控制產生了純色畫素的錯覺,抖動進一步欺騙眼睛和大腦,從而擴大了感知色調。

在之前的文章中我還提到,穿過液晶元件的光可能源於「周圍環境產生的光透過鏡面背板反射,透過背光自發光,或兩者兼有。」如今,幾乎所有LCD顯示器都利用了背光,其最初由一排冷陰極螢光燈管(CCFL)組成,但近年來被LED陣列取代,實際上「LED電視」是一個誤導的行銷術語(基於LED的是背光,而非它本身的顯示元件)。更先進的LED背光採用了各種尖端技術,包括替代全光譜「白光」LED的RGBLED三元組群,以及在LED陣列內選擇特定區域「局部調光」照明控制等,進一步擴展顯示器的色域、對比度範圍和其他特性。

#### **OLED**

三星是讓「LED電視」這一行銷用語被濫用的「罪魁禍首」,恕我直言,我猜這可能是因為三星想要模糊其 LCD和OLED顯示器的區別。彼時其

圖2:LG在CES上展示了一系列弧形OLED顯示器。(圖片來源: David Benjamin)

主要競爭對手LG剛開始加強OLED的促銷力度(三星在2010年推出Galaxy S系列,成為首批採用OLED的智慧型手機製造商之一)。實際上,這兩種技術是完全不同的,OLED具有自發光特性(用一個更文雅的術語就是「發射性電致發光」),顯示器根本不需要單獨的背光。因此,OLED顯示器非常薄並具有高度的柔軟性,在今年的消費電子展上,LG甚至展示了一款可以「卷起」的OLED電視。

你可能認為OLED沒有背光所以功耗會比LCD同類產品更低,嗯,你是對的……只不過是有時候。再次引用我2010年關於OLED報導,「當以黑色顯示為主時OLED提供了極佳的功耗;但當以淺色顯示為主時,例如常見的在淺色或白色背景上顯示深色文本,它們的電池消耗可能會顯著高於LCD/背光組合。」這也解釋了為什麼Android、Chrome OS、iOS及相關應用程式多採用「暗」顯示模式。

### QLED

幾年前,三星在CES上展示了基於QLED的原型,現在它已有多種型號投入生產。由於相似的命名,你可能很自然地認為「QLED」是「OLED」的變體,事實上這兩種技術是完全不同的。首先,QLED不會自發光,它像LCD一樣,需要補充背光(因此名稱

中包含「LED」)。但是,它用稱之為 「量子點(QD)」的結構代替了LCD的 液晶矩陣(因此名稱中有表示量子點的 「Q」)。引用維基百科的解釋:

量子點是尺寸只有幾奈米(nm)的 微小半導體粒子,具有與較大的LED 粒子不同的光學和電子特性,是奈米 技術的核心主題。很多類型的量子點 在被電或光激發時會發光,其頻率可 以透過改變量子點的大小、形狀和材 料來精確調整,從而實現多種應用。

量子點的特性介於體半導體(bulk semiconductor)和離散原子或分子之間。它們的光電特性隨尺寸和形狀而變化。直徑為5~6nm的較大量子點發射較長波長的光,產生橙色或紅色等顏色;較小的量子點(2~3nm)發射較短波長的光,產生藍色和綠色等顏色,具體的顏色和尺寸根據量子點的不同組成而變化。

正如你所瞭解的,QLED由於採用了成熟的LED背光技術,因此從技術上來說是某種程度的改進,而不是完全的創新。雖然量子點的螢幕材料是一個突破,但它從概念上退回(至少在我看來)到了CRT中使用的紅-綠-藍磷光點螢幕。糟糕,我不小心暴露了年齡……

#### Micro LED

「Micro LED」聽起來不像「QLED」,

# 技術縱橫

更不像「OLED」,但從概念上講它實際上更接近三星的這兩種技術。三星曾推出一款146时的Micro LED大顯示器,這絕對可以稱之為「The Wall」,今年又新推出了更合消費者胃口(雖然很勉強)的75时型號(當然,隨後還會有更大的219时型號)。以下是我在三星新聞稿中發現的最有趣的敘述:

由於Micro LED具有模組化特性, 該技術可提供螢幕尺寸的靈活性,使 使用者可以定制螢幕尺寸以適應任何 房間或空間。利用添加Micro LED模 組,使用者可以將顯示器擴展到他們 想要的任何尺寸。Micro LED的模組化 功能未來還允許用戶創建9×3、1×7 或5×1等不規則尺寸的終極顯示器, 以滿足其空間、美學和功能需求。

無論螢幕的大小和形狀如何,三星的Micro LED技術還可以最佳化內容。即使多添加幾個模組,三星的Micro LED顯示器也可以進行縮放以提高解析度,同時保持畫素密度不變。此外,Micro LED可以支援從標準的16:9到21:9的寬螢幕電影,甚至支援非常規長寬比(如32:9,甚至大援非常規長寬比(如32:9,甚至1:1)的所有內容,而影像品質不打任何折扣。

最後,Micro LED顯示器不具擋板,可添加更多的模組,模組之間也沒有邊框。這種無縫技術可以實現令人驚歎的無邊泳池的效果,使Micro LED顯示器可以優雅地融入任何生活環境。

具有消費者定制靈活性的確很不錯,但我對Micro LED模組化沒什麼興趣,主要原因是從製造的角度來看,三星可以提供同樣的靈活性。想想看……撤開子畫素和其他的影響因素不談,這些最新的「8K」解析度電視包含3,320萬個畫素(7,680×4,320)。相信我,我認為他們的工廠生產不出完全沒有畫素缺陷的顯示器,尤其是現在還處於其生命週期的早期。良率降低,成本(因此價格)勢必將比現在高出許多。

值得慶幸的是,由於畫素密度高,普通消費者幾乎察覺不到隨機散佈在顯示器上的缺陷(或很少),當然,對於超近距離檢視螢幕的電視迷則要另當別論了。然而,太多的缺陷,特別是緊密聚集在一起的缺陷,是不可接受的。同樣要考慮的是,顯示器還會受到半導體元件良率動態的影響。顯示器(晶片裸片)較大時,每片的顯示器數就會減少(每

個晶圓的裸片),出現缺陷的概率也會呈指數增加。因此,如果三星確實可以用多個較小的模組組裝Micro LED大顯示器,那麼這將為他們帶來巨大的收益(成本更低、價格更低)。

那麼,Micro LED到底是什麼?這次我可以說它與OLED一樣,具有一個自發光結構(無背光)。然而,它本質上是無機的(還沒有想到嗎?OLED中的「O」表示「有機」)。以下是來自維基百科的解釋:

Micro LED顯示器由形成各個畫素 元件的微縮LED陣列組成。與廣泛使 用的LCD技術相比,Micro LED顯示 器具有更好的對比度、回應時間和能 效……與傳統LCD系統相比,OLED 和Micro LED都能大大降低能耗。與 OLED不同,Micro LED基於傳統的 Gan LED技術,提供比OLED產品高 達30倍的總亮度,以及更高效的效率 (以lux/W衡量)。

開始寫這篇文章時我沒打算寫成一本書,但如果繼續寫下去,就真的會變成一本書了。所以就到這兒吧,但我仍然會密切關注這些和其他有趣的顯示技術的發展。一如既往地,歡迎與我分享你的任何想法!

# 耗蝕性雷射釋放材料應用於 RDL優先扇出封裝優勢

作者: Ramachandran K. Trichur、Rama Puligadda、Tony D. Flaim, Brewer Science

半導體產業正處於一個新時代,當摩爾定律成為IC擴展的指導原則時,設備擴展不會繼續以與過去幾年相似的速度提供成本降低或效能改進這些優勢了。擴展到7奈米以下節點的成本正在大幅上升,並且需要進行大量的投資到下一代光刻解決方案的資本財設備和研發支出這兩個方面。由於在為消費電子、行動性設備、雲端運算、汽車和各種其他應用開發的產品和服務方面取得了重大躍升,對更高

效能表現、更小外形、更密集的積體和更低成本設備的需求正在以前所未有的速度增長。雖然半導體產業不斷推進 積體電路的擴展,但它也轉向採用先進的封裝技術來提高 效能和積體,同時降低成本。

多元異質模組整合所面臨的多個挑戰之一是彌合晶片級和板級可用I/O的差距。在晶片級,隨著I/O密度的增加,趨勢一直在縮小晶片尺寸,因此需要創造性的封裝技術將晶片

以如此高的I/O密度連接到電路板上。眾多不斷發展的封裝技術在設備的多元異質模組整合中發揮著重要作用,其中晶圓級扇出(WLFO)封裝技術已成為主導製程。WLFO製程已經針對商業經營化部署多年,採用簡單的單晶片設計,重構晶圓一側的單個製作導線重新分佈層(RDL),以及厚式重構晶圓組的稀薄矽區域,進而產生較厚的封裝。

最近,為了解決一般使用者對效能、積體和外形尺寸的需求,扇出封裝的設計和製程複雜性不斷增加,包括多晶片封裝、積體被動元件、多重RDL層,以及3D扇出封裝,同時不斷減小×、y和z方向的封裝尺寸。隨著晶片尺寸,製程複雜性和封裝複雜性的增加,產量成為扇出封裝製程的關鍵要素。傳統的扇出製程採用晶片優先/RDL其後方法,其中使用已知的良好晶片建造重構晶圓,然後在重構晶圓頂部建造RDL。

隨著重構晶圓和RDL的複雜性增加,該製程容易在RDL層級產生損耗,其中已知良好的晶片(KGD)標示位在不良的RDL位置。產能減少可能是由於幾個因素造成的,包括晶片位移、熱膨脹錯配、光刻對準不良等,導致在封裝製程中損失昂貴的KGD。

為了避免在封裝過程中損壞KGD,開發了一種稱為RDL優先/晶片其後的扇出封裝的備用扇出製程,其中RDL首先建造在載體晶圓上,KGD放置在已知良好的RDL位置之上,繼而避免了KGD的損失。

RDL優先製程還為RDL提供了更精細的線/空間維度方面的其他優勢,以便為更密集的設備積體提供複雜的路徑。在本文中,借助舉出幾點解決在製程中遇到的一些關鍵挑戰的事例,可說明支援RDL優先扇出封裝開發的耗蝕性雷射釋放材料的優勢。

# 扇出晶圓級封裝(FOWLP)技術

如上所述,FOWLP技術大致有兩個主要的製程類別;晶片優先/RDL其後扇出和RDL優先/晶片其後的扇出封裝。兩種製程路徑中的進階積體方案都需要使用臨時接合材料的某種形式載體輔助製程。

#### 晶片優先/RDL其後的FOWLP

晶片優先扇出製程採用晶圓重建製程,在這個製程中,會從原始裝置晶圓中揀出KGD並置於基板上,然後以模壓樹脂包覆成形創造一種稱為重構晶圓的異質而高應力的基板材。如果重構晶圓的厚度小於350µm,則這些晶圓由於內部應力較大而表現出嚴重的彎曲,並且具有高溫能力的臨時接合材料對於使用製程流程支撐重構晶圓是必不可少的,以減少彎曲和減輕設備中的處理問題,以及修正在RDL生產期間用於光刻的對準期間所產生的配準錯誤。

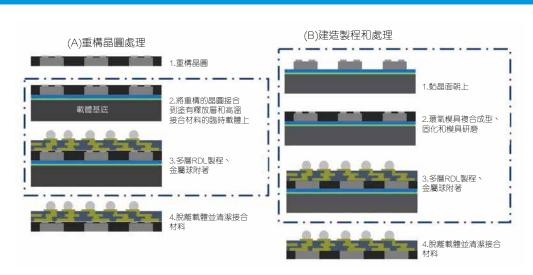

晶片優先製作流程有兩個通用製程路線,即重構晶圓處理和建造製程及處理。圖1顯示了這兩種製程路線的一般示意圖製程。這兩種路線的主要差異發生在重構晶圓建造期間,在製程路線A,重構晶圓處理中,晶圓建造在單獨的載體上,然後轉移到塗有高溫臨時接合材料和釋放層的第二載體上,用於隨後的RDL建造和組裝。在製程路線B中,晶片附著、重構、RDL建造和組裝過程發生在塗有高溫相容的臨時接合材料和釋放層的單個載體上。

用於晶片優先型製程的臨時接合材料的主要挑戰包括翹 曲控制、模具移位、溫度穩定性等,這些在先前的出版物中 已經加以解決。晶片優先扇出製程現在大量使用,越來越多 地用於支持行動電子應用。

圖1:使用載體輔助方法顯示針對晶片優先流程的兩種主要方法的通用流程。(A)重構晶圓處理及(B)建造製程和處理,虛線框狀區域顯示了臨時接合材料在該製程中的作用。

圖2: RDL優先/晶片其後的製程的製程示意流程圖,虛線框狀區域顯示了臨時接合材料在該製程中的作用。

### RDL優先/晶片其後的FOWLP

圖2顯示了RDL優先的FOWLP過程的示意流程圖。晶片附著的RDL層製程和組裝製程會在塗有釋放層的暫時載具上完成,通常,玻璃載體塗有釋放層,然後是完成一系列製程步驟,最後創造成為RDL層。這些步驟會重複多次,最終創造出一個多層RDL結構。在RDL製程完成之後,晶圓經歷組裝製程步驟:包括晶片附著、模製和模具研磨,然後釋放載體。在晶圓級上,對於RDL優先類型的製程慣用載具分離方法是,採用電射分離機制。許多代工廠和委外封裝測試(OSAT)正在開發這種製程,可針對用在晶圓級和面板級的進階積體整合。

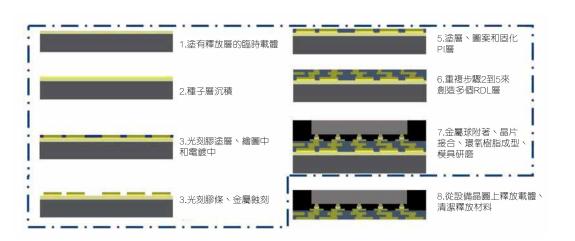

#### RDL優先製程中耗蝕性釋放材料的關鍵要求

耗蝕性雷射釋放層塗覆在載體上,作為後續的分佈層、晶 片附著、組裝和模製過程皆在其上所進行的分層。該材料 用作為基礎材料,所有其他層附在其上建造而成,而不只 是用於接合層或釋放層等的單一功能。與晶圓優先製程相 比,RDL優先製程在犧牲層上更為嚴峻,因為在早期RDL 成形階段中,整面的這個釋放層會開放接觸製程化學品, 取決於具體的製造流程,釋放層需要對金屬種子層和/或聚 合物介電層具有良好的黏附性。釋放層還必須具有良好的 耐化學性,以抵抗光刻化學物質、金屬蝕刻化學物質和開 面測。此外,剝離層需要在聚醯亞胺(PI)固化步驟中經受 長時間的高溫處理,並且避免在高溫和高壓模具附接製程 和模具的環氧樹脂模製期間流動。另外,釋放層需要在PI 固化步驟中經受長時間的高溫處理,還要避免流動發生在 高溫和高壓黏晶製程和模具的環氧樹脂模製期間。圖3顯 示了RDL第一製程的耗蝕性釋放層的關鍵要求,請注意, 將這種材料稱為耗蝕性釋放層並不能確實傳達這種材料所 具有的所有基本功能。

#### 塗覆製程

耗蝕性雷射釋放層必需與晶圓及面板級塗覆技術相容。 這些材料應提供優異的塗層品質,並均匀分佈TTV在整個基 材上。相關的一些風險是針孔缺陷、去濕斑點、厚度不均匀 等。這些塗層異常將對下游製程產生不利影響。

例如,針孔缺陷和去濕斑點將導致塗覆在釋放層頂部上的接續層(PI層或PVD金屬)直接接觸到載體基底板,這就是藉由針孔及去濕斑點所致。這將導致較差的脫離效能,因為在載體和金屬或PI層之間將不存在釋放層來提供釋放功能用到缺陷區域上。如果釋放層塗有不均匀的厚度,這將影響釋放功能並可能影響釋放層的雷射吸收能力,導致在脫離過程中高能雷射光傳輸到主動元件表面,從而對設備產生潛在的傷害可能性。

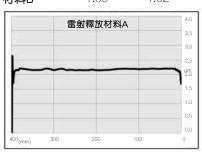

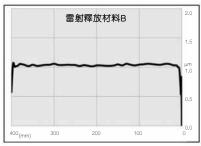

由Brewer Science開發的耗蝕性雷射釋放層可以相容於與用於晶片級應用的旋塗製程和用於面板級應用的槽模塗覆製程。這些材料塗覆在玻璃晶圓和面板上,具有優良的均匀性,且沒有任何缺陷,圖4顯示了使用槽模塗覆製程塗覆的耗蝕性釋放材料A和B的面板級均匀性。

圖3:RDL第一製程的耗蝕性釋放層的關鍵要求。

| 範圍   | 平均   | 均匀性    |

|------|------|--------|

| 0.06 | 2.18 | ±1.42% |

| 0.04 | 1.04 | ±2.13% |

根據70×470裸玻璃上的塗層所得的結果

圖4:使用槽模塗佈製程塗覆的耗蝕性釋放材料A和B的面板級塗層均匀性。

#### 附著

耗蝕性雷射釋放材料必須非常牢固地黏附到玻璃,有機物如PI,以及使用PVD製程諸如鈦(Ti)和銅(Cu)沉積的金屬。較差的黏合強度將導致在分佈層的脫層或在組裝製程中,建造設備基板材的的分離。除了釋放層的特性之外,還已知特定的金屬沉積製程對黏合強度有影響,應遵照金屬沉積的最佳典範執行以改善對釋放層的黏著性。

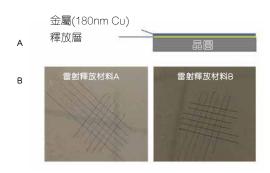

本文測試了雷射釋放材料A和B與PVD Cu的黏著性,此 測試是採用ASTM-D3359標準化的交叉影線測試。圖5顯示 了Cu在兩種材料上的交叉影線黏著性測試的結果,較差的黏 著性將導致由交叉影線圖案產生的Cu方塊的剝離,但是這裡 結果顯示在測試之後所有Cu方塊與釋放層的絕佳黏著性。

### 熱效應及機械穩定性

耗蝕性釋放層的關鍵要求包括透過建造過程的熱穩定性 和機械穩定性。建造在釋放層頂部的RDL層要求固化溫度超 過250℃,每層約1~3小時,因此,3層RDL結構會使釋放層 暴露在長達9小時的高溫製程循環中。在熱循環期間,釋放 層不應軟化或分解,並且必須保持硬性和穩定。

耗蝕性雷射材料A和B都是熱力和機械穩定的材料。材料A是一種熱塑性材料,其玻璃化轉變溫度 $(T_g)$ 高達320℃,熱分解溫度 $(T_g)$ 為410℃。材料B是熱固性材料, $T_g$ 為270℃,並且在低於 $T_g$ 的溫度範圍內不顯示 $T_g$ ,這些特性導致材料在PI固化期間的高溫製程中不軟化或分解。

#### 化學穩定性

耗蝕性釋放層需要承受苛刻的化學條件,其大部分是在開放面中,因為在RDL的建造期間,釋放層將與包括濕蝕刻化學物質在內的若干製程化學物質直接接觸。典型的化學物質涉及溶劑、金屬蝕刻化學品、抗蝕劑脫離劑、電鍍化學

物質和其他組裝製程化學物質。在製程過程的化學池中,釋放層不得溶解、損失厚度或污染,研究耐化學性的常用方法 是目視檢查,化學品暴露前後釋放層的厚度測量,以及在塗 有釋放層的基板材浸入之前和之後,測量鍍液速率或製程池 的蝕刻速率的變化,以檢測任何污染或將釋放層浸入池中。

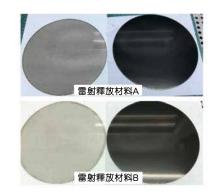

藉助在矽(Si)晶圓上塗覆釋放層然後將晶圓浸入相應的化學物質中,進行目視檢測和/或厚度測量,得以研究出釋放層的化學穩定性。對於涉及目視檢查的測試,只有一半的晶圓浸入化學物質中,並觀察浸沒區域對塗層的任何不利影響(顏色變化、黏著力損失、厚度損失等),並與未浸入在化學物質中的區域做比較。圖6顯示了雷射釋放材料A和B的化學暴露研究結果,表1顯示了對材料A進行的其他耐化學性研究。

### 雷射脫離

雷射脫離是RDL優先製程的首選脫離方法,是導向完全建造設備晶圓釋放的關鍵製程。該過程中的任何偏移或缺陷都將導致昂貴的設備晶圓產量損失,雷射脫離製程的重點是不損壞設備晶圓,具有高生產量的脫離製程,並且殘留物最少。文獻指出,在以UV雷射為基礎的脫離中,消融主要是由於有機雷射釋放材料的光化學破壞而發生,而不是使用較

圖5:(A)黏著試驗的試驗結構的示意圖和(B)Cu在兩種釋放材料A和B的交叉影線黏著試驗的結果。

圖6:耐化學性研究(A)晶圓部分浸入化學池中的示意繪圖和(B)暴露於化學物質後塗有雷射釋放材料A和B的晶圓的照片。

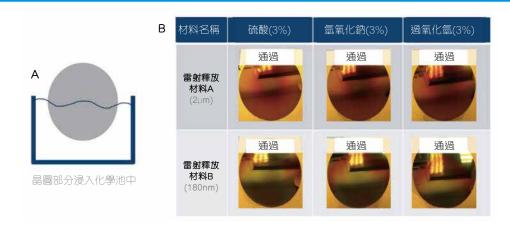

長波長雷射源在消融中發生的光熱破壞。耗蝕性雷射釋放層吸收UV電射光並化學解離以從設備晶圓中釋放載體。光化學消融製程對設備晶圓的熱影響較小,並且消融發生在載體和雷射釋放材料的介面處。Brewer Science開發的耗蝕性雷射釋放材料與市場上可用於晶圓和面板脫離的所有常見UV雷射脫離工具(308nm、343nm和355nm)相容,圖7顯示了使用355nm電射波長的材料A和B的脫離結果。

#### 後期脫離清潔

雷射脫離製程完成後,必須清除設備晶圓上的所有釋放 層殘留物。材料A是熱塑性釋放層,它與溶劑清潔製程和等 離子體清潔製程相容。材料B是熱固性釋放層,它與等離子 體清潔製程相容,後期脫離清潔過程的重點方面是使用經濟 有效且短的清潔程序完全去除殘留物。

使用平行板等離子蝕刻機來清潔材料A和B的雷射脫離殘留物。表2顯示了用於等離子體清潔的配方。兩種材料都易於使用氧等離子體作清潔。材料A也可以使用NMP或二氧戊環作為溶劑在旋轉或噴霧清潔工具中使用溶劑清潔進行清潔。

從上述對RDL優先扇出封裝的製程要求列表中,可以很容易地認為雷射釋放層是實現RDL優先製程的關鍵材料之一。 文章中的範例展示了雷射釋放材料A和B的效能,但Brewer Science還開發了其他幾種配方和厚度變化,以滿足各別客戶和製作流程的需求。一個這樣的材料變化被用於在合作夥伴端展示完整流程RDL優先製程,並且這個完整流程製程的結果最近也已發表。使用玻璃載體在晶圓級上進行實驗,其中除了建造多層RDL,還跟著進行晶片附著、模製、脫離、清潔和晶粒的單個化。對最終設備的電效能進行測試,以確認在雷射脫離過程中模員或電路沒有發生損壞。

隨著我們超越摩爾定律的時代並進入「不只是摩爾」的 時代,每個電子設備都整合了多種功能,用於感測、處理、

| 化學品            | 之前的厚度       | 之後的厚度       | 註釋 |

|----------------|-------------|-------------|----|

| NMP90℃ 25分鐘    | 2.44±0.19µm | 2.61±0.11µm | 通過 |

| 2%氨10分鐘        | 2.39±0.03µm | 2.34±0.03µm | 通過 |

| 2.5% TMAH 10分鐘 | 2.44±0.13µm | 2.24±0.32µm | 通過 |

| PGMEA 10分鐘     | 2.29±0.33µm | 2.31±0.33µm | 通過 |

| 緩衝液HF3分鐘       | 2.27±0.01µm | 2.27±0.02µm | 通過 |

表1:使用雷射釋放材料A擴展耐化學性研究。

圖7:使用355nm雷射源脱離雷射釋放材料A和B。

| 材料  | 厚度    | 氣體<br>(sccm)       | 時間<br>(秒) | 電力<br>(W) | 壓力<br>(mTorr) | 直流偏壓<br>(DC-Bias) | 結果 |

|-----|-------|--------------------|-----------|-----------|---------------|-------------------|----|

| 材料A | 2µm   | O <sub>2</sub> -50 | 600       | 150       | 100           | 396               | 清潔 |

| 材料B | 180nm | O <sub>2</sub> -50 | 60        | 150       | 100           | 396               | 清潔 |

表2:用於雷射釋放材料A和B的等離子體清潔的配方。

資料傳輸、顯示等,多元異質模組整合和系統級封裝(SiP)技術在滿足一般使用者的需求方面發揮重要作用。行動電子產品、物聯網應用和其他連結的服務將繼續推動半導體產品的效能要求,先進的IC封裝製程將越來越成為滿足這些需求的必要條件。作為先進材料供應商和半導體供應鏈不可分割的一部分,Brewer Science深知材料的轉型創新是維持和支持下一代電子設備發展的關鍵。

# 電源完整性還有新招?

作者: Raj Nair, Planet Analog

保證電源完整性(Power integrity,PI) 最常見的方法是增加片上去耦電容, 此方法特別適用於解決電壓下垂和其 他動態電源差分變化。在負載電路 中,本地電容吸收瞬態電源電流,有 助於滿足瞬態電荷需求。但由於電容 是「無功」電路元件,只有在電壓變 化時才會提供電荷,這裡i(t)=C(dv/ dt),所以,電容透過提供電荷來降低 電壓下垂,而且僅在發生電壓下垂時 才會提供電荷。

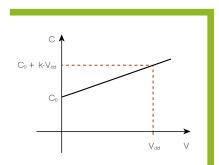

現在來看看依賴於電壓的電容元件,其電容隨電容極板間的電壓而變化,如**圖1**所示。

電容C是所施加的電壓V的線性函數,而電荷量Q呈平方變化,所以,在依賴於電壓的電容中,電荷量隨電壓的變化率dQ/dV部分地與kV成正比。當電容充滿電時,與恆定電容相比,依賴於電壓的電容中電荷以更快的速率( $C_0$ +kV>C)耗盡。因此,當遷移的電荷量 $\Delta$ Q相同時,在依賴於電壓的電容中,電壓降低較少。這一點也可以理解為:在給定工作電壓 $V_{dd}$ 時,使恆定電容的電荷儲存量為 $C_1V_{dd}$ 。

在獨立於電壓的電容中,遷移的

圖1:電容是電壓的線性函數。

電荷量  $\Delta$  Q可以透過電壓變化為 $V_{n1}$  來反映。而對依賴於電壓的電容,相同的  $\Delta$  Q電荷遷移量產生電壓 $V_{n2}$ 和電容 $C_{n2}$ (小於 $V_{dd}$ 處依賴於電壓的電容)。根據電荷守恆定律, $\Delta$  Q很小時, $C_1\Delta V_1 \approx C_2\Delta V_2$ ,其中  $\Delta$  V是電壓的減小量。由於 $C_2$ (= $C_0$ +k $V_{dd}$ )大於  $C_1$ (透過二次充電儲存相同的總電荷),  $\Delta$   $V_2$ 小於  $\Delta$   $V_1$ ,最終得出了一個大致的關係式:

$$\frac{\Delta V_2}{\Delta V_1} = \frac{C_1}{C_2} \tag{1}$$

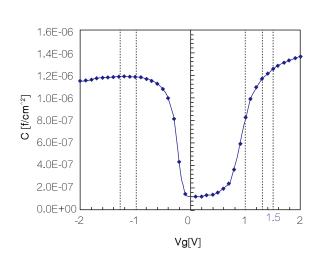

如圖2所示,在以累積耗盡模式工作的MOSFET元件中(圖中右側),電容隨電壓顯著變化。因此,在給定工作電源電壓下可以設計和偏置元件,以顯示其電壓依賴性,儘管該特性可能受頻寬限制。相較於在傳統的通道反轉模式下工作的元件,工作於累積耗盡區的MOSFET元件表現出更低的閘極氧化物洩漏。由於提供了對偏置元件的激勵,這種去耦電容在IC中被廣泛採用。(請注意:英特爾130nm節點以下的晶片被認為採用了這種片上去耦電容。)

# 電壓可變電容中的電荷和能量

表現出**圖2**所示行為的電容中包含的電荷和能量可以推導如下:

由於 $C=C_0+kV$ ,電壓可變電容的電荷量Q為:

$$Q = \int dq \int (C_0 + kV) dv$$

$$= C_0 V + \frac{1}{2} kV^2$$

(2)

假設當Q=0時V=0。當k=0時,等式簡化為Q=CV;當 $C_0$ =0,Q=½kV²=½CV。電壓可變電容中包含的電荷量呈二次方上升;當基極電容為零時,是在電容不依賴於電壓的情況下電荷量的一半。因此,選擇 $C_0$ 和k必須確保兩種情況下儲存的總電荷量相同。

類似地,在電壓可變的電容內, 能量可以從因電荷增加而增加的工作 中得到:

$$dw = V \cdot dq$$

因為 $C = C_0 + k \cdot V$ 電壓可變電容能量 為:

$$W = \int dw = \int V(C_0 + kV) dv$$

=  $\frac{1}{2}C_0V^2 + \frac{1}{3}kV^3$  (3)

同樣,當k=0時,上述運算式簡化為恒定電容儲存能量的已知運算式。 有趣的是,令C<sub>0</sub>=0和k=2C/V,使儲存的總電荷與恒定電容相同,由電壓可變電容能量運算式得到值(2/3)CV<sup>2</sup>,與恒定電容相比高出六分之一的能量。

此外,對於上面討論的電容依賴於電壓的情況,還可以對表現出的電源電壓雜訊進行比較,如下所示:

$$\Delta Q = C_1 \Delta V_1 = \int_{V_{ad}}^{V_{ad}} (C_0 + kV) dV$$

$$= \frac{1}{2} k(V_{n2}^2 - V_{dd}^2)$$

$$= \frac{2 \cdot C_1}{2 \cdot V_{dd}} (V_{n2} + V_{dd}) \cdot (V_{n2} - V_{dd})$$

$$\rightarrow \Delta Q = C_1 \Delta V_1 \approx 2 \cdot C_1 \cdot \Delta V_2$$

然而,電壓可變電容對電源完整性的影響是一個複雜的現象,並不像圖1或公式(1)所示的那樣容易建模。如圖2所示,元件電容隨電壓的變化源於半導體材料內的非理想電荷分佈。隨著施加的偏壓增加到元件呈現正電壓係數的區域,元件的兩個閘極氧化物隔離部分的電荷之間的有效距離從其無偏值變小。這導致元件極板之間的有效電隔離減小,電容因之增加,因為電容值C=6A/d。

在元件電氣特性產生的這種變化 中完成工作,元件以其固有電氣性質 變化的形式儲存電荷和能量。對於平 行板電容,彈簧將極板連接到剛性表 面,並使它們彼此分開。隨著極板上 差分電荷增加,極板被彼此吸引,減 小了它們之間的距離,增加了有效電

圖2:採用深亞微米製造製程的MOSFET元件,從反轉模式到累積模式,其閘極電壓與 電容的關係。

容。同時,能量也儲存在因極板運動 產生的彈簧位移中。因此,需要一個 電物理分析模型。

上述的討論強調了之前提到的真實物理建模的必要性。在依賴於電壓的去耦電容中,透過固定的分佈電容來近似有效電容值,提供足以用於佈

局規劃的合理、準確的雜訊估計。最常見的情況是,在任何新的製造製程或元件偏置配置中,電路功能和雜訊的矽驗證無法被替代。因此,在電壓可變的情況下,片上去耦電容效應必須在矽中進行驗證,根據其物理行為擷取元件行為並進行建模。

# 使用分貝要謹慎

作者: Bob Witte, Signal Blue LLC總裁

分貝在電子系統中的應用很常見,包括射頻(RF)、音訊,以及現在經常提到的訊號完整性。現在許多工程師都已經在用分貝思考了,但在時域領域的情況可能會不同。

由於我的主要背景是射頻領域, 我更傾向於將分貝與射頻測量關聯 起來,儘管分貝最初是由電信系統 工程師用來定義音訊頻率的。在20 世紀初,貝爾系統裡有個概念叫做 標準電纜哩數(Miles of Standard Cable·MSC),用來表示一種規格為 19號的電話電纜在經過1英哩後的損耗特性。這個概念最後演變為傳輸單位,定義為:

$$TU = 10log\left(\frac{P_{m}}{P_{r}}\right)$$

其中,Pm是測量功率,Pp是參考功率。後來,TU被命名為分貝,表示貝爾的十分之一(貝爾以Alexander Graham Bell的名字命名)。請注意這支持貝爾(bel)的定義,僅表示兩個功率之比的對數。TU實際上過去是一個

傳輸單位,後來才被命名為分貝。由此人們可能很容易將分貝視為像伏特(V)或安培(A)這樣的度量單位,但它實際上是一種用以10為底數的對數來處理兩個數位比率的方法。另外,你可能注意到,分貝早期縮寫為「db」,但現在常用「dB」表示。

有興趣深入瞭解分貝歷史的讀者可以查閱American Radio History網站,該網站儲存了許多經典技術出版物,包括1922年及以後的《Bell System Technical Journal》。我花了一些時

間閱讀早期關於電話的文章,對那時 人們對電子原理的理解程度深感驚訝 並白愧不如。

### 功率和電壓

嚴格來講,分貝是用於定義功率比:

$$A_{dB} = 10log\left(\frac{P_2}{P_I}\right)$$

大多數工程師很快就能學會一些 幫助他們進行分貝計算的經驗法則, 例如:

- 功率無變化,分貝值為0dB;

- 功率因數為2,分貝值為+3dB 或-3dB;

- 功率因數為10,分貝值為+10dB

或-10dB。

雖然分貝被定義為功率比,但分 貝公式常被用作測量電壓,比如均方 根(RMS)電壓:

$$P = \frac{V^2}{R}$$

$$A_{dB} = 10log\left(\frac{V_2^2/R_2}{V_I^2/R_I}\right)$$

$$A_{dB} = 20log\left(\frac{V_2}{V_1}\right) + 10log\left(\frac{R_1}{R_2}\right)$$

根據以上算式可以匯出一個類似 的公式:

$$A_{dB} = 20log\left(\frac{I_2}{I_I}\right) + 10log\left(\frac{R_2}{R_I}\right)$$

在恒定阻抗(電阻)系統中,比率R<sub>1</sub>/R<sub>2</sub>的值為1,可以從等式中約除,剩下的就是我們所熟悉的電壓分貝公式:

$$A_{dB} = 20log\left(\frac{V_2}{V_I}\right)$$

由於電氣工程中的許多訊號都是 以電壓測量,因此將分貝應用於電壓 值而不是功率值會更便利。

- 電壓無變化,分貝值為0dB;

- 電壓因數為2,分貝值為+6dB

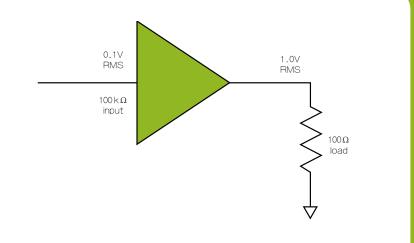

圖1: 具有100kΩ輸入阻抗的放大器驅動100Ω負載。

或-6dB;

• 電壓因數為10,分貝值為+20dB 或-20dB。

# 謹慎使用分貝

但是,忽略 $R_1/R_2$ 可能會導致嚴重混淆,因此一定要謹慎。例如,**圖1**表示一個具有高輸入阻抗( $R_1$ ,100k $\Omega$ )和低輸出阻抗的放大器,其驅動的負載阻抗為100 $\Omega$ ( $R_2$ )。輸入電壓為0.1VRMS,輸出電壓為1VRMS,電壓增益為10。用分貝來表示,電壓增益為20log(10)=20dB。

再來看功率,輸入功率為(0.1)²/100k=0.1µW,而負載功率為(1.0)²/100=10mW。當利用功率值計算增益時,得到10log(10mW/0.1µW)=50dB。根據所使用的是電壓還是功率,會得出不同的放大器增益(dB),由於電壓比的分貝公式是根據功率比的分貝公式計算得出,所以我們期望其結果也是一致的。

因為忽略了阻抗差異,實際上可以假定阻抗總是相同的,但在圖1中情況並非如此。再回頭看電壓方程式中的 $R_1/R_2$ ,計算圖1中因阻抗變化缺失的因數。

即  $10\log(R_1/R_2) = 10\log$  (100k/100)=30dB,這個值表示了上

述兩個增益值之間的差異。

許多系統都具有一致的阻抗。例如,許多射頻系統始終圍繞50Ω系統阻抗來構建,所有輸入、輸出和傳輸線阻抗均相同。在這種情況下,功率和電壓分貝方程可以互換使用,分貝值也一致。

但在其他系統中,阻抗是變化的。 當然,可以使用R<sub>1</sub>/R<sub>2</sub>校正因數進行補 償,但更常見的做法是只選擇電壓或 只選擇功率來避免產生任何問題。現 在,可能有純粹主義者堅持分貝是嚴 格依照功率來定義(的確如此),所有分 貝計算都必須考慮到這一點。

我表示同意,然而我經常看到工程師們嚴格按照電壓和20log(V<sub>2</sub>/V<sub>1</sub>)來計算而沒什麼問題,這樣做的益處是不必調整阻抗也可以使用分貝值,但他們不得不時刻提防與功率計算混在一起,這個例子很好地說明了工程師如何有效利用數學上不純粹卻有實用價值的方法。

以上介紹了一些分貝的概念,強調了利用電壓進行分貝計算的潛在問題。下一篇將描述如何使用分貝來表示絕對值。

例如,公共功率参考值為1mW 時,得到的dBm值(相對於1mW的 分貝)。

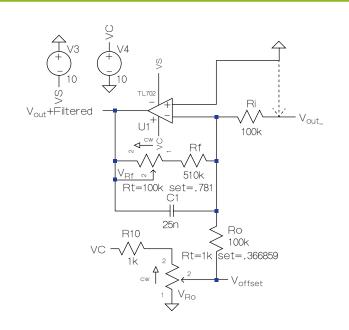

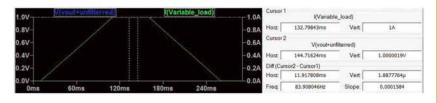

# 數位電位器模擬對數錐度以準確設置增益

作者: Stephen Woodward, EDN特約作者

數位電位器(dpot)是一種常見的元件,採用各種封裝、電阻和解析度。但是,除了電阻和設置之間的常規線性函數,它並無其他效用。不過,對於需要寬動態增益調整範圍(例如數十倍頻程)的應用來說,這會造成一些問題。

以一款放大器為例,使用8位元 (1/256)解析度電位器,將其增益設置為0~10,000(80dB)。當電位器設置與電阻(線性錐度)成線性關係時,數位電位器設置與增益也成線性關係。在256個電位器設置中,每個步進都表示約40的增益幅度增加(即增益步進為0、40、80、120、160等)。

對於8或以上的數位電位器設置(增益>300),這為增益設置提供了不錯的解析度,可以實現每個步進1dB或更低的增益控制。但是,當設置值低於8時,增益解析度大幅降低。例如,如果需要將增益設置為100或以下,就沒有辦法讓所需的值具有有效的精準度,因此只能選擇80或120左右的值。

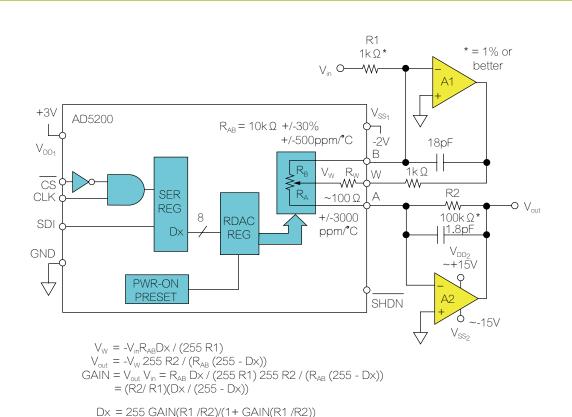

若使用一個帶對數錐度(log taper) 的準確、穩定、高解析度數位電位器 (電阻對數與設置成正比),就很容易安 排增益控制電路,在整個調整範圍內提 供恆定的解析度(增量單位:dB)。遺憾 的是,目前並沒有具備出色解析度(例 如步進小於6dB)的對數數位電位器。 但並非全無用處。圖1所示的設計實例就採用了一個普通的線性錐度電位器(例如,ADI提供的價格便宜的雙極AD5200),實現了近似的對數增益控制。

如果Dx表示游標設置(0~255),可以採用分段求解的方式,輕鬆得出放大器增益Vout/Vin與Dx的設計公式。

首先,求解作為Vin函數的游標電 壓(Vw):

$Vw = -VinR_{AB}Dx/(255 R1)$

接下來,求解作為Vw函數的 Vout:

圖1:線性數位電位器模擬對數錐度。

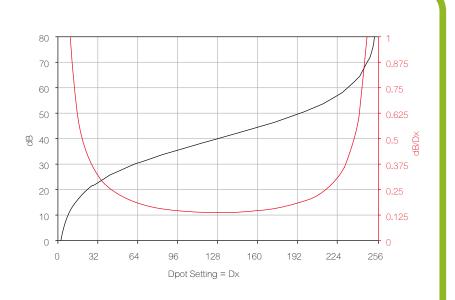

圖2:dB增益(左側y軸)和增益設置解析度(右側y軸)與Dx(x軸)之間的關係。

$Vout = -Vw \ 255 \ R2/(R_{AB}(255-Dx))$

然後,將公式1和2結合在一起:

增益=Vout/Vin=-Vw255 R2/(RAB(255- $(Dx) / (-Vin R_{AB} Dx/(255 R1))$ 增益=(R2/R1)(Dx/(255-Dx)) Dx=255增益(R1/R2)/(1+增益(R1/R2)) 毫無疑問:

dB(增益)=20 $Log_{10}((R2/R1)$ (Dx/(255-Dx)))

和

增益=10<sup>dB/20</sup>

由此得到:

$Dx = 255 \ 10^{dB/20} (R1/R2)/$

$(1+10^{dB/20}(R1/R2))$

認真看看得出的增益公式,可以看 到這些有意思的地方:

1. Dx/(255~Dx)的近似對數性質。如 **圖2**所示,當R2/R1=100、Dx=8 時,得出的增益=~10dB; Dx=23 時,增益為20dB; Dx=128時, 增益為40dB; Dx=232時,增益為 60dB; Dx=247時,增益為70dB。 在整個60dB=1,000~1的範圍內,增 益設置的解析度仍然不超過1dB,這 一點尤其重要。此外,Dx=0時,增 益設置為0,同時Dx=255選擇開環。

- 2. 採用電位器游標作為輸入端子的策 略有效地將游標觸點移動到放大器 A1的反饋回路中(圖1),從而避免 了成為誤差項,改善了增益設置的 時間和溫度穩定性。

- 3. 同時,在A1回饋和A2輸入(**圖1**)端 使用RAB電阻元件可以將RAB公差 和溫度係數(tempco, AD5200中分 別為±30%和500ppm/℃)與靈敏度 進行比較,使R1和R2成為增益設置 精度的唯一決定因素。

如果需要高於8位元(1/256)的解析 度,可以在拓撲中採用10位元AD5292 這樣的元件,得到4倍的高增益設置 精準度。

謹記,增益公式中出現255時,要 替換為1023,或者,採用如下更通用 的方程式,其中N代表位數:

$Dx=(2^{N}-1)$ 增益(R1/R2)/(1+增益(R1/R2))R2)) EDN

# 一個雜亂無序的掃頻VCO電路板佈局

作者: John Dunn, EDN資深部落客

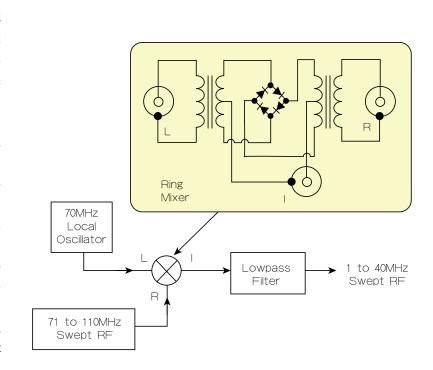

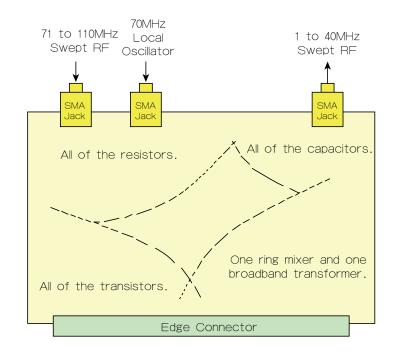

我們的專案是設計一個具有1MHz~40MHz射頻(RF)掃頻輸出的訊號產生器。由於無法製作一個可涵蓋40MHz~1MHz頻率範圍的可掃描單一訊號源,因此我採用以下方案來設計。

該設計採用一個工作於71MHz~ 110MHz的掃頻壓控振盪器(VCO),頻 率範圍僅為1.55~1。該振盪器的輸出 對固定頻率70MHz本地振盪器進行外 差,然後採用低通濾波器提取差頻。

這種方法非常有效,除了在設計過 程中發生以下的意外。

我為我的環路混頻器(我稱之為「混音卡」)畫了一個原理圖,並將原理圖提供給指定公司的設計和繪圖部門,他們專門安排了電路板佈局人員來配置。最後我看到的草圖如圖2所示。

他將所有電阻放在一個角落,所有電容放在第二個角落,幾個電晶體放在第三個角落,環形混頻器和寬頻變壓器放在第四個角落,然後將所有這些元件透過細銅箔線連接起來。整個設計最後看起來就像一鍋新鮮出爐的粉絲,有點無序的粉絲。

當我告訴這個小夥子他的設計不可接受時,他回答說,「嘿!我已經這樣做了25年了!」。他看起來不過30歲左右,這意味著幼稚園時期他就是個神童了,我對此深表懷疑。

我推翻了他的設計,將我用於製作麵包板的佈局給他,堅持讓他依這個來佈局;顯然,一開始我就應該這樣做。

最近,一位煩惱的同事談起了他的類似遭遇,這讓我想起這件事。有一天這種事情也可能發生在你身上,不要氣餒,只要堅定信心,就能處理好。

圖1:掃頻VCO原理框架圖。

圖2:一個糟糕且無法使用的佈局。

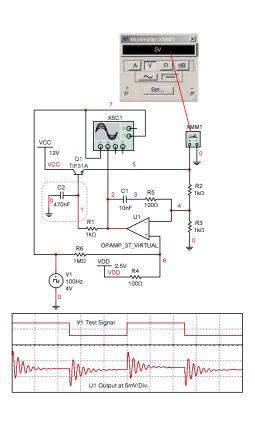

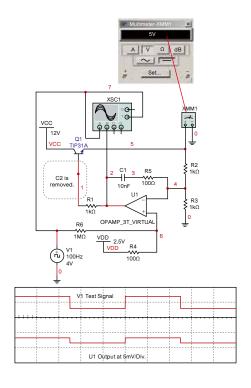

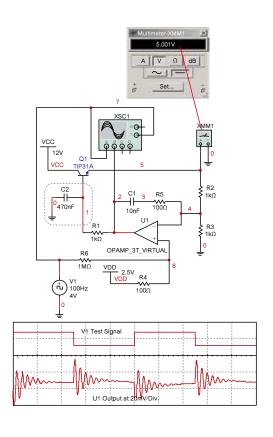

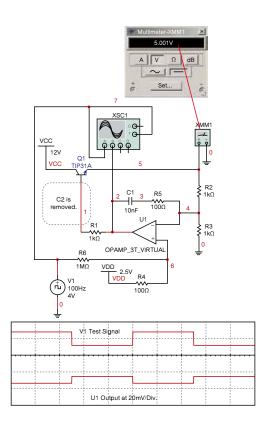

# 利用階躍激發進行穩定性測試

作者: John Dunn, EDN資深部落客

透過網路分析儀測量得到的波特圖可以用於測試反饋回路的穩定性,從而確定和判斷增益裕度和相位裕度。這個儀器確實很有用,但它太昂貴了,對於我們中間一部分幾近「貧困」的從業者來說,可能需要其他更便宜的方法,而這個方法可能就是階躍激發(step excitation)。

階躍激發的基本思路很簡單,就是將一個很小的方波干擾注入反饋回路,然後觀察反饋回路對干擾的回應。注入干擾的位置,以及觀察位置可以自行決定。可以有多個干擾點或觀察點,以下本文僅給出四個示例草圖。

在**圖1**中,當通過R6送到誤差放大

器U1非反相輸入端的方波激發對理想 穩壓器產生輕微干擾時,U1的輸出為 欠阻尼振鈴波形。可從而得出結論, 即使在最好的情況下,該回饋環路的 穩定性也很差。

在圖2中,除了拿掉了C2之外,一切都與圖1相同。不明智地加入C2,雖然可能產生某種類型的EMI抑制效果,但對環路穩定性卻有不利影響,會產生糟糕的增益裕度和相位裕度,看來有人並不明瞭這一點。

我們並不知道增益裕度和相位裕 度的具體值是多少,但很顯然沒有C2 時,結果會漂亮得多。

在圖3中,又重新加上電容C2。 但這次階躍激發通過R6注入到誤差 放大器的求和點,結果U1輸出端的 欠阻尼振鈴波形看起來比**圖1**中的波 形更差。

在圖4中,再次拿掉C2,穩定性 又變好了。看來不能用C2了。

這裡展示的只是一個非常簡單的 例子,但以兩種截然不同的方式注入 了方波干擾,即階躍激發。實際的回 饋系統會更複雜,有許多可能的注入 點,也有許多觀察點,需要檢查所有 這些點。

選擇的注入點對正在檢查的反饋 回路應該沒有影響,或者影響很小, 可忽略不計。

對上述的電路來說,R6阻值為1M 已經夠大了。 **EDD**

圖1:採用階躍激發的理想穩壓器。

圖2:採用相同的穩壓器和激發,卻表現出更好的穩定性。

圖3:相同的穩壓器,但階躍激發不同。

圖4:相同的穩壓器和激發,但表現出更好的穩定性。

# 壓擺率和上升時間:不盡相同

作者: Bob Witte, Signal Blue LLC總裁

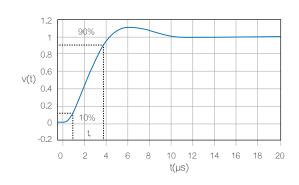

在之前那篇《什麼是訊號頻寬?》(編註:本文已刊登於EDN Taiwan 3月號雜誌)的文章中,瞭解了上升時間和頻寬之間的關係。關於上升時間的討論經常會引出一個問題:上升時間與壓擺率(SR)是同一件事嗎?

先來看壓擺率,壓擺率的概念與上升時間類似,但有一些重要區別。如圖1所示,階躍回應的上升時間被定義為波形從終值的10%變為90%所需的時間。(有時上升時間被定義為20/80%)請注意,上升時間透過波形大小的百分比來定義,與所涉及的電

壓無關,例如圖1中的波形具有大約 3 us的上升時間。

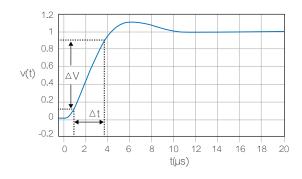

壓擺率定義為波形的變化率,與 斜率相同。它可以利用算式 $\Delta$ V/ $\Delta$ t得 出,如**圖**2所示。

■2顯示了10%和90%兩個點之間的 △V/△t,實際上這個算式可以在波形的任何位置進行,因為我們只是在尋找斜率。請注意,壓擺率以V/s(或更常見的V/µs)為單位,實際上也表示它是用來衡量每單位時間電壓的變化率。

從圖2中,可以計算出壓擺率:

Slew Rate =

$$\frac{\Delta V}{\Delta t} = \frac{0.8V}{3\mu s} = 0.267 \frac{V}{\mu s}$$

現在來設想圖2中的階躍響應增加 10倍的情況,從0V變為10V,而上升 時間仍然是3µs。則壓擺率計算如下:

Slew Rate =

$$\frac{\Delta V}{\Delta t} = \frac{8V}{3\mu s} = 2.67 \frac{V}{\mu s}$$

果然,當上升時間相同時,壓擺 率會增加10倍,因為電壓的變化速 度快很多。這突出了上升時間和壓擺 率之間的關鍵差異:上升時間無關乎

圖1: 階躍回應的上升時間是從終值的10%變為90%所需的時間。

圖2:壓擺率是波形的斜率,計算式為 $\Delta V/\Delta t$ 。

圖3:正弦波在過零點處具有最大壓擺率。

絕對的電壓水準,僅表示波形變化所 需的時間,而壓擺率則描述電壓的變 化率。

# 正弦波示例

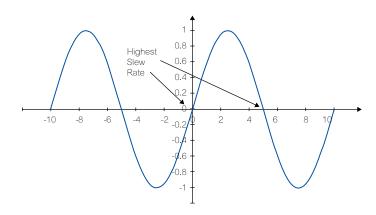

對於輸入為正弦波的情況(如圖3所示), 可以應用一些基本的微積分算式得到 壓擺率。

$$v(t) = V_p \times \sin(2\pi f t)$$

壓擺率是波形的斜率或導數。

Slew Rate =

$$\frac{dV}{dt} = V_p \times 2\pi f \times \cos(2\pi f t)$$

當餘弦函數達到其最大值1時,壓擺率也最大。同樣,當餘弦函數達到最小值-1時,壓擺率也最大只是符號相反,圖3還顯示出最大壓擺率點出現在正弦波的過零點處。

$$SR_{MAX} = 2\pi f V_p$$

毫不奇怪,最大壓擺率與波形頻率 及其幅度成正比。波形越大轉換速率越 快。波形頻率越高轉換速率也越快。

# 放大器規格

到目前為止,本文一直在討論電壓波 形的壓擺率,描述電壓變化的速率。 壓擺率通常被用來描述放大器的性 能,它定義了訊號在放大器輸出端的 轉換速率。它指的是放大器的最大壓 擺率,對於上升斜率和下降斜率波形 可能會不同。 放大器的頻寬通常受壓擺率性能的限制。全功率頻寬(FPBW),也稱為大訊號頻寬,定義為放大器在其最大輸出電壓擺幅下可產生的最高頻率。假設FPBW受放大器最大壓擺率的限制,那麼可以透過重組上述的算式來計算FPBW。

$$FPBW = \frac{SR_{MAX}}{2\pi V_{o}}$$

# 應用

壓擺率是運算放大器的一個重要參數,尤其是在處理大輸出擺幅時。

可能聽說過電源與壓擺率相關,它 描述電源的電壓或電流從一個設置值 轉換為另一個值的速率。通常這與測 試系統中的可程式設計電源有關,透 過不同的測試條件來排序。電壓和電 流壓擺率可以是測試激發的一部分。 也就是說,由於某些電壓或電流在兩個特定值之間可以受控轉換,可以利用它來測試元件的性能。或者,利用壓擺率來抑制被測元件的浪湧電流。

可能還會見到壓擺率與電磁干擾(EMI)相關。具有尖銳邊緣的訊號易於輻射高頻成分,眾所周知,諸如數位 邏輯元件和開關電源穩壓器這類快速開關電路會產生EMI。為了抑制EMI,一部分元件提供了壓擺率控制,允許設計人員選擇邊緣速率並控制輻射。有些情況下,也可以利用添加外部電路來降低邊緣速率,例如,電路設計人員可以在數位時脈電路中增加RC電路來降低壓擺率和輻射。

本文概述了壓擺率與上升時間的關係。它們的確有相似之處,但最關鍵的區別在於壓擺率描述了波形的實際變化率。 (EM)

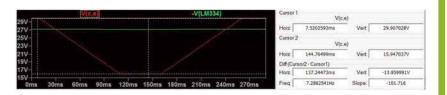

# 一種改進的新型閉鎖電源開關

作者: Anthony Smith, EDN

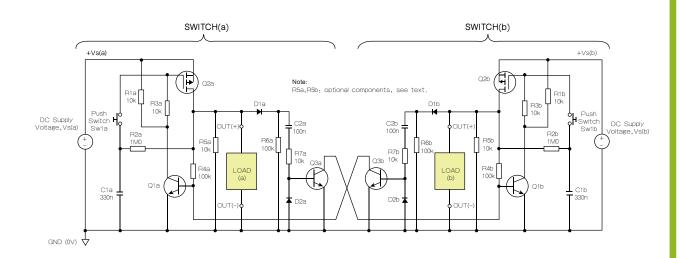

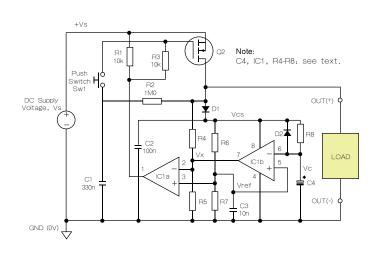

EDN之前的一篇設計實例文章《Latching power switch uses momentary pushbutton》介紹了一個相對簡單的電路,其中的暫態按鈕可以像機械閉鎖開關一樣工作。這篇文章得到了大量的讀者回饋,在回饋中,有讀者追問是否有可能將電路調整為:(a)交叉耦合電路,其中的兩個開關可以互相「抵消」;(b)「時間延遲」電路,其電路將在預定時間關斷。本文將嘗試實現這些建議的電路。

#### 交叉耦合閉鎖開關

■1顯示了以交叉耦合方式連接的兩個開關電路,其中每個開關透過其自身的暫態按鈕開啟和斷開,而且當一個開關開啟時,另一個會斷開。由於具

有相互抵消的特點,這種電路適於汽車指示燈等應用。

這兩個開關電路完全相同並彼此鏡像,即R1a與R1b提供相同的功能,Q1a與Q1b功能完全相同,依此類推。除了額外的交叉耦合元件(C2、D1、D2、R6、R7和Q3)之外,每個開關電路都與《Latching power switch uses momentary pushbutton》中介紹的基本電路大致相同,如該文章中的圖1(a)所示,其中有基本電路如何工作的詳細說明。需要注意的是,根據負載性質的不同,R5是可選的;而且對於馬達這類負載,可能需要在OUT(+)端子和負載之間連上一個阻塞二極體。

為了理解交叉耦合是如何工作的,

假設Switch(a)當前關閉,Switch(b)打 開,這使得Q1a和Q2a關閉,Q1b和 Q2b都導通並透過R3b和R4b相互提供 偏置。如果此時按下暫態按鈕Sw1a, 則Q1a和Q2a導通,並且Switch(a)鎖 定到其通電狀態。在Q2a導通的瞬間, 電流脈衝通過D1a、C2a和R7a傳遞到 Q3a的基極,導致Q3a瞬間導通,並 短暫地將Q1b的基極短路至0V。Q1b 和Q2b此時都關閉,Switch(b)鎖定到 關閉狀態。Switch(a)現在鎖定在其通 電狀態,並將保持此狀態直到按下任 一按鈕開關。如果此時按下Sw1b,則 Q1b和Q2b接通,Switch(b)鎖定到打 開狀態,Q3b瞬間接通,使Q1a和Q2a 關斷。

流經Q3的短暫電流脈衝的時間長

# **Design Note**

採用 4mm × 4mm × 1.82mm BGA 封裝的低 EMI、 Silent Switcher、1.2A µModule 穩壓器 Austin Luan

#### 引言

在擁擠的應用電路板中,為高效能 DC/DC 負載點轉換器預留的空間極為狹小。不僅如此,在元件安裝密度很高的情況下,電磁干擾 (EMI) 也是一個重大的問題,其限制了可接受電源解決方案的電場。LTM®8074 µModule®穩壓器可輕易地滿足這些限制因素。該元件結構精小,使之能夠安置在 PCB 正面的有限空間,或者憑藉其扁平的外型佈設在 PCB 的背面。LTM8074 採用 Silent Switcher® 架構,使其無需額外的濾波或遮罩元件便能通過嚴格的 EMI 測試,從而簡化設計和生產。

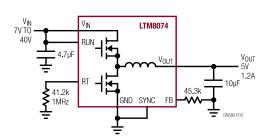

#### 1.2A Silent Switcher µModule 穩壓器

LTM8074 為一款完整的超低 EMI、高電壓輸入和輸出、DC/DC 降壓型開關電源。該元件在符合 RoHS 標準的扁平 4mm×4mm×182mm 表面黏著型 BGA 封裝中內建了控制器、電源開關、電感器和所有的支援元件(圖1),因而可以利用 PC 板底面的未用空間,以實現高功率密度負載點調整。

LTM8074 可操作於 3.4V 至 40V 的輸入電壓範圍,輸出電壓為 0.8V 至 15V。輸出電壓經過精準的調整,並提供達 1.2A 的輸出電流。高效率和耐熱性能增強

•

圖 1: LTM8074 採用 Silent Switcher 架構以創建一款內建於纖巧型封裝的完整低雜訊解決方案

型封裝實現了卓越的熱性能和高功率密度。如圖 2 所示,LTM8074 在承受負載的情況下之外殼溫度升幅極小,並具有低熱阻。

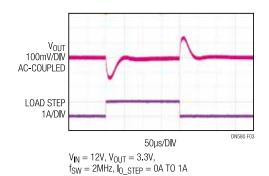

内部控制器的峰值電流模式控制架構可實現快速瞬變響應和良好的迴路穩定性。圖 3 所示為快速瞬變響應和在輸出電壓的低峰至峰電壓偏差。

設計透過優化的内部回授迴路補償得以簡化,該補償可在眾多操作條件下、以及採用各種輸出電容器時提

圖 2:在室溫 (23°C) 條件下, LTM8074 在滿負載時 具有低溫升 (12V 輸入至 5V/1A 輸出)

圖 3: LTM8074 採用極少的輸出電容器 (2 × 4.7μF 陶瓷電容器) 實現了快速瞬變響應 (12V<sub>IN</sub>, 3.3V<sub>OUT</sub>)

供充足的穩定性裕量。LTM8074 採用 Silent Switcher 架構,可將輻射發射降至最低,使其能夠輕易地滿足嚴格的電磁相容性標準。

#### 適合安裝在狹小的空間

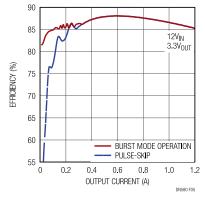

所有的支援零組件均整合於 LTM8074 精小的封裝內,因而簡化了佈局設計並縮減解決方案尺寸。僅需輸入和輸出電容器、頻率和電壓設定電阻器即可構成完整的設計。圖 4 和圖 5 分別顯示典型的應用電路及其效率。

儘管 LTM8074 的 μModule 設計可造就幾乎獨立的直接替代型穩壓器,不過許多設計參數可輕易地調整以滿足特定應用的需要。輸出電壓和操作頻率可利用電阻器設定,而且操作頻率可被設定為與一個外部時脈同步。另外,LTM8074 還具有可編程軟啟動、輸出電壓追蹤、電源良好指示器和致能控制、以及多種導通模式選項,包括脈衝跳躍模式、Burst Mode®操作和展頻調變,以進一步優化輕負載效率和 EMI 性能。

圖 4:7V 至 40V 輸入、5V<sub>OUT</sub>/1.2A 設計 所需的元件極少

圖 5:LTM8074 的典型效率設計所需的元件極少

**產品手冊下載** www.analog.com/LTM8074

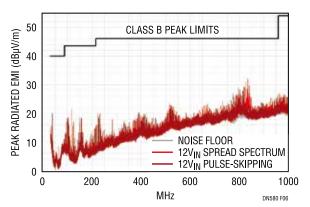

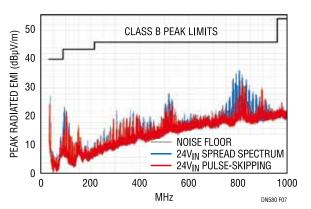

#### 超低雜訊: CISPR 22 Class B

切換開關穩壓器自然會產生輻射 EMI, 因為它們的運行需要在相對高的頻率下經歷高 dl/dt 過程。LTM8074的低 EMI 性能源於其內建的專利 Silent Switcher 架構,而並未依賴繁瑣的 EMI 緩解方法,例如:降低切換開關頻率、增設濾波器電路、或安裝遮罩。如圖 6 和圖7 所示,滿足 CISPR 22 Class B 等輻射 EMI 標準,並無需採用外部電路或特殊的佈局方法。

圖 6:對於 12V<sub>IN</sub> 至 3.3V<sub>OUT</sub>/1.2A 的 EMI 性能與 CISPR 22 Class B 要求之比較 (3m峰值、垂直天線、無 EMI 濾波器)

圖 7:對於 24V<sub>IN</sub> 至 3.3V<sub>OUT</sub>/1.2A 的 EMI 性能與 CISPR 22 Class B 要求之比較 (3m、峰值、垂直天線、無 EMI 濾波器)

#### 結論

LTM8074 是覆蓋寬廣輸入和輸出電壓範圍的精小型 1.2A 負載點 µModule 穩壓器。該元件採用 Silent Switcher 架構實現內建的低 EMI 性能和方便設計的可調整能力,以滿足眾多應用要求,包含可攜式裝置以至於高組裝密度工業電路板均在其列。

電子郵件:support@morrihan.com

網 址:www.morrihan.com

#### 圖1:交叉耦合開關獨立鎖定但相互抵消。

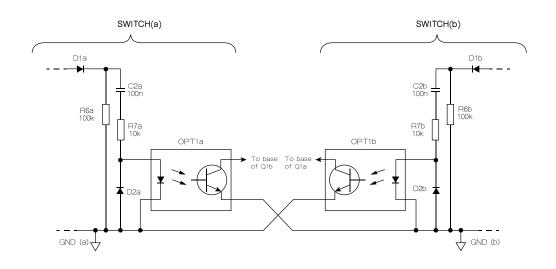

圖2:光電耦合器實現了完全隔離的交叉耦合開關。

度由C2-R7時間常數決定,這個時間要足夠長以使對端的MOSFET完全關斷。記住,當Q1關斷時,儲存在Q2閘極上的電荷必須透過與R3串聯的R1完全釋放。一些大電流MOSFET的閘極電容為幾十奈法(nF),因此當R1=R3=10kΩ時,閘極可能需要幾毫秒才能完全放電。現在,當C2=100nF且R7=10kΩ時,Q3將Q1的基極鉗位約5ms,這個時間應足夠長以關閉大多數的P通道MOSFET。

在上述電流脈衝結束時,C2上的

電壓將大致等於電源電壓+Vs。如果沒有二極體D1,該電壓將保持Q1導通,從而防止開關關斷。有了D1,阻斷動作將允許開關正常關斷,這樣當Q2關斷時,C2上的電壓將透過R6-D2-R7這個路徑放電。

儘管Switch(a)和Switch(b)是相同的,但它們並不需要同樣的電源電壓,即+Vs(a)和+Vs(b)不需要相等並且可以來自不同的源。但由於圖1中的電路要實現交叉耦合,Switch(a)和Switch(b)必須共用一個共地回路

(0V)。對於不能共用共地回路的應用,Q3a和Q3b可以用光電耦合器代替(如圖2所示),它允許每個開關有自己的接地回路,與另一個開關電隔離。大多數普通光電耦合器應該都可以正常工作,但要注意,光電LED需要比電晶體更高的驅動電壓。因此如果電源電壓+Vs比較低時,可能需要降低R7的值(並相應地增加C2的值)。

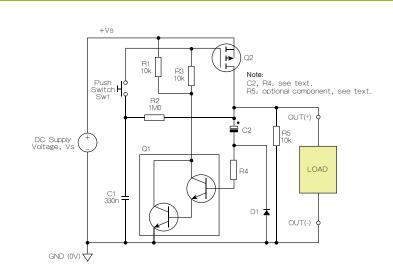

#### 具有定時輸出的閉鎖開關

某些應用可能會需要可以在預設的一

#### 設計實例

段時間之後自動關閉的閉鎖開關。 圖3顯示了一種非常簡單的實現定時輸出的方法,其中Q1從單個電晶體改為達靈頓對(Darlington pair,或稱達靈頓電晶體,Darlington transistor),並在Q2的汲極和R4之間插入電容C2。和前述電路一樣,暫態按鈕Sw1用於控制電路。當開關閉合時,Q2導通,並透過C2和R4向達靈頓基極提供偏置電流。電路此時鎖定在通電狀態,Q2透過Q1保持導通。

C2此時開始充電,而C2和R4連接處電壓下降,下降速率很大程度上取決於C2-R4時間常數。當電壓下降時,透過R4傳輸到達靈頓基極的電流也會下降;最終,當達靈頓集電極電流變得太小,無法為Q2提供足夠的閘極驅動時,MOSFET關斷。開關此時恢復到未鎖定狀態,C2開始透過D1放電,負載與R5並聯(若已安裝R5)。請注意,只需按下按鈕,開關即可在定時「導通」期間的任何時刻解鎖,無需等到輸出超時。

由於一對達靈頓對提供了高電流增益,因此可以採用較大的R4值(大約幾M $\Omega$ )來產生較長的時間常數。由15V電源供電的測試電路產生的「導通」時間,範圍從大約9秒(C2=1 $\mu$ F,R4=1M $\Omega$ )到超過15分鐘(C2=10 $\mu$ F,R4=10M $\Omega$ )。將C2增加到100 $\mu$ F,「導通」時間甚至可以超過兩小時。

儘管該電路足以滿足那些要求不高的應用,但它仍有幾個可能限制其適用性的缺點。達靈頓對的電流增益對於確定電路的時間常數十分重要(該增益可能因元件和溫度的不同產生很大變化)。所以對於那些需要精確控制「導通」時間的應用,該電路並不適合。同樣,電源電壓的變化也會影響「導通」的時間。

此外,達靈頓對的集電極電流逐漸減小也將導致MOSFET慢慢關閉。

圖3:對基本開關電路做小改動以實現預設定時輸出。

圖4:輕負載時較長的關斷時間也許可以接受。

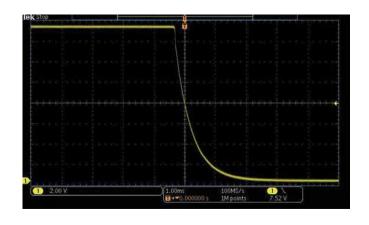

從圖4的波形圖可以看出這種結果,圖中顯示了由15V電源供電、具有500 Ω 負載、採用FDS6675A MOSFET作為Q2,且R4為1MΩ的電路輸出。請注意輸出從15V(導通狀態)轉換到0V(關斷狀態)幾乎需要3ms的時間,對於輕負載而言,這麼長的關斷時間也許是可以接受的,但對於開關大電流的MOSFET卻遠非理想。

圖5對上述電路進行了改進,其中達靈頓對由兩個開汲/開集比較器 (IC1)取代,R5由潛在分壓器R4-R5取代。R6-R7分壓器產生參考電壓Vref (比較器電源電壓Vcs的恒定分數),為兩個比較器提供穩定的參考電壓。

第一次按下開關時,Q2導通,為 負載供電,同時正向偏置D1,為比較 器提供電源電壓Vcs。此時,如果R4/ R5=R6/R7,電壓Vx將略大於Vref, 使IC1a的輸出電晶體導通。其輸出變 為低電平(接近0V),從而透過R3為Q2 提供閘極偏置。

電路現在鎖定在「導通」狀態,定時電容C4開始透過R8充電,C4的電壓Vc呈指數上升。在Vc剛剛超過Vref時,比較器IC1b跳閘,其輸出電晶體導通,將V×拉低至0V。IC1a的輸出電晶體此時關斷,而且由於Q2不再有閘極驅動,MOSFET關斷,開關解鎖。C4此時透過D2-R6-R7路徑比較快

圖5: 改進後的電路可提供精確時序、快速開關,以及抵抗電源電壓變化的能力。

Time delay comparator, IC1b:

$$V_C = V_{CS} (1 - e^{-\frac{t}{\tau}}), \text{ where: } \tau = R8 \times C4$$

Trip-point occurs when:  $V_C = V_{ref}$

$$V_{ref} = k. V_{CS}$$

, where:  $k = \frac{R7}{R6 + R7}$

Equating

$$V_{CS}$$

(1 –  $e^{-\frac{t}{\tau}}$ ) with k.  $V_{CS}$  gives:

Output 'on' time:

$$t_{ON} = -\tau \cdot ln(1-k)$$

$$or: t_{ON} = - \left( R8. \ C4 \right) \ln \left( \frac{R6}{R6 + R7} \right) \ \left( seconds \right)$$

| TIMING COMPONENTS                                                                     |      | OUTPUT 'ON' TIME(s) |             |

|---------------------------------------------------------------------------------------|------|---------------------|-------------|

| C4                                                                                    | R8   | Measured            | Theoretical |

| 1µF                                                                                   | 1ΜΩ  | 1.22                | 1.16        |

| 10µF                                                                                  | 1ΜΩ  | 11.1                | 11.6        |

| 100µF                                                                                 | 1ΜΩ  | 162                 | 116         |

| 100µF                                                                                 | 10ΜΩ | 1,728               | 1,163       |

| Note: IC1 = TLC393, R4 = R6 = $10k\Omega$ , R5 = R7 = $22k\Omega$ , and $+Vs$ = $15V$ |      |                     |             |

#### 圖6:圖5所示電路的時序公式和測試結果。

速地放電。與上述的簡單電路一樣, 只需按下開關即可隨時解鎖開關。

阻塞二極體D1提供雙重功能。當Q2關斷時,它將R2與儲存在C2上的電荷隔離,從而確保開關正確解鎖。此外,當開關關斷時,它可以防止C2(和C4)利用負載快速放電。這為比較器在Q2關斷時保持供電提供了短暫的時間,從而確保電路以有序的方式關閉。為比較器供電的是開關輸出而不是電源電壓,這滿足了本文介紹的所有電路的基本要求,即(就像機械開關一樣)「關斷」狀態下的功耗為零。

**圖6**顯示了電路的時序公式,以及 當IC1=TLC393、R4=R6=10kΩ、 R5=R7=22kΩ、+Vs=15V時的測試 電路的結果。請注意Vcs並不在公式中,因此「導通」時間基本上不受電源電壓變化的影響。

可以看到,測試結果和理論結果很好地吻合,除了當C4=100µF時產生的「導通」時間比計算得出的時間長很多。這很可能是由於測試所採用的電解電容內部產生了洩漏(非電解類型用於1µF和10µF測試)。若採用合適的元件,可以實現超過1小時的「導通」時間。

忽略D1上的壓降,比較器電源電壓與直流電源電壓大致相同(Vcs≈+Vs),這會影響可用的比較器類型。TLC393雙微功率比較器因極小的功率要求和極低的輸入偏置電流(通常

圖7:電路的改進極大地提高了從"導通"到"關斷"的轉換速度。

為5pA)而成為理想選擇,儘管它們僅限於16V左右的電源電壓。LM393具有相同的功能,並可在高達30V的電源電壓下使用,但由於其電源電流大於TLC393,輸入偏置電流也相對較大(通常為-25nA),這會影響C4的充電速率。選擇R4-R7的數值時,要確保V×和Vref不超過比較器的高共模電壓限值(對TLC393和LM393來說,大約比Vcs低1.5V)。

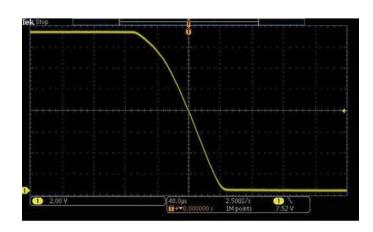

除了為定時輸出提供相當精確的控制以外,改進型電路從「導通」

狀態轉換到「關斷」狀態的速度比圖3所示的簡單電路也要快得多。 圖7所示的波形圖顯示了測試電路的輸出,該電路由15V電壓供電,並採用與上述簡單電路相同的500Ω負載和FDS6675A MOSFET。與圖4中稍顯遲滯的回應相比,從完全「導通」到完全「關斷」的開關時間大大縮短,只有大約100μs。

#### 選擇元件

上述電路對使用的雙極型電晶體和二

極體並沒有特殊要求,只要提供最大電源電壓,大多數具有良好電流增益的NPN雙極型電晶體都是適用的。在最大汲源電壓、電流處理和功耗方面,P通道MOSFET的額定值必須與高階驅動電路中的任何元件相當。需要注意的是,某些類型MOSFET的最大閘源電壓限值遠低於汲源電壓額定值。

例如,IRFR9310的最大汲源電壓額定值為-400V,而閘源電壓被限制在±20V。如果應用需要非常大的電源電壓,則可能需要在MOSFET的閘極和源極之間連接一個保護齊納三極體,以便將閘極電壓鉗位到安全水準。

儘管所有電路中都使用了按鈕開關,實際上按鈕開關是可以用磁簧繼電器(提供磁啟動開關)或其他類型的暫態觸點來代替。唯一的要求是觸點必須相對於電源軌電「浮動」。

最後,請記住圖5中的IC1必須是開汲或開集類型。此外,要注意大阻抗和敏感節點使電路易受雜訊影響,可能導致錯誤觸發和某些不可預測的行為,因此要避免「雜亂」的結構,並在必要時使電路免受EMI和RFI的影響。

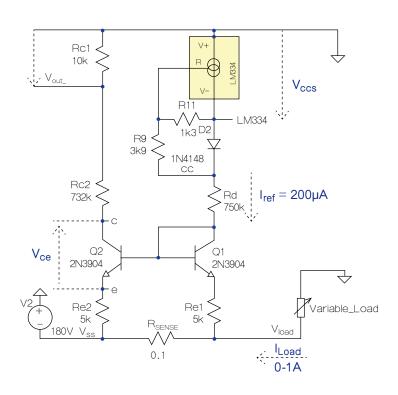

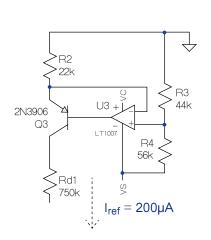

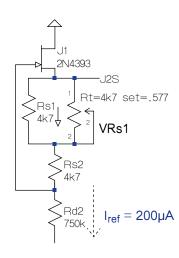

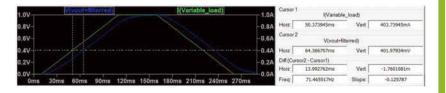

## 採用低壓電晶體進行高壓電流檢測

作者:Seagan Yi-O'Kelly,EDN特約作者

專用整合電路的應用使電流監控變得 越來越簡單。各種電流監控整合電路 隨時買得到,而且多數情況下都工作 得很好,還有各種儀表放大器也是如 此。使用離散元件構建電流監控器似 乎顯得多餘,然而在某些情況下,特 別是在有現成的低壓元件時,使用離 散元件的電路來進行電流監控可能是 最好的方法。

本設計實例中的電路用於監控伺服

系統+180/-180V電源的兩個電源軌中的電流。圖1顯示了用於監控負軌的電路相關部分,監視正軌的電路只需用pnp設備替換npn即可。採用價格便宜的雙電晶體和1%電阻來設置Iref,以及Re1和Re2可獲得最佳效果。Rsense應為0.1%並且具有足夠的額定功耗。

圖1所示電路和所有類似拓撲結構的設計靈感均來自電流鏡拓撲結構,以及Re2上的電流隨Rsense上的電流、相

應地Rc1上的電壓隨Rsense上的電壓線 性變化的這個概念。

該電路的作用依賴於Re1和Re2。 讓Iref相當小而Re2和Re1相當大,當 Re2和Re1的值相等時,相對於Rsense 上的電壓,發射極的電壓將增加。當負 載在無負載和滿負載之間變化時,這 將反過來減小輸出設備上Vce的變化。

因此,審慎而明智地選擇Iref、 Re1、Re2、Rc2和Rc1可以防止Q2進

#### 設計實例

圖1:負軌監控電路。

圖2:用恒流源產生Iref的替代解決方案。

入飽和狀態並且不會超過電晶體的最大工作電壓。請記住,hoe=I(集電極)/ $_{VA(早期電壓)}$ 意味著減少IC的變化也會減少 $_{\beta}$ 的變化,從而改善線性度。RC是RC1和RC2之和,因此比率RC1/RC確定無負載時Vout-處的偏移。滿載時Rsense上的電壓決定了Re2和RC1的電流變化,

圖3:設置FET偏置,使啟動時Iref不會 導致Vce或Vds超過最大值。

從而決定了Vout-的滿量程輸出。一旦 Iref值建立,就可以很容易計算出Rc 和Rd上所需的無負載電壓。透過使用發射極電阻,可以顯著降低Vce變化對Q2的β的影響,而且從模擬資料可以看出,β的變化對負載電流和輸出電壓之間相關性的影響相對較小。鑒於這

#### 設計實例

些結果,採用類似於威爾森(Wilson)電流鏡的配置似乎並沒有必要。

- 圖2和圖3顯示了用恆流源產生Iref的替代解決方案。如果Vss穩定且沒有波紋,則可以省略恆流源產生器,並且可以利用設定Rd值來提供Iref。

- 圖4所示的電路反轉了Vout-,消除了偏移,並將輸出調整到所需範圍,還可以過濾輸出端出現的電源波紋或負載 尖峰。若配以帶有ADC的微控制器,則可以將電路簡化為僅反轉Vout-。

如果滿載時 $V_{Re1}$ 至少比 $V_{Rsense}$ 大10倍,那麼Q2將不會進入飽和狀態,並且:

$$V_{Rsense} = (Iload + Iref) \times Rsense$$

(1)

$$V_{Rel} = 10(V_{Rsense}(full\ load))$$

(2)

|ref=|<sub>Re1</sub>,無負載,即|load=0, |那麼:

$$Re1=V_{Re}/Iref=Re2$$

(3)

Vccs是恆流源兩端的電壓, $I_{Re1}$ 約等於Iref,Vbe可以為0.6~0.65V:

$$Rd = (Vss - (Vccs + Vbe_{(O1)} + V_{Re1}))/Iref$$

(4)

Vce是Q2上無負載時所需的最大電 $\mathbb{E} \cdot I_{pop}$ 約等於Iref,那麼:

$$Rc = (Vss - Vce)/I_{(Re2)} \approx (Vss - Vce)/Iref$$

(5)

Vout-無負載時所需的失調電壓決定 了Rc1的值:

$$Rc1 \approx (RcxVout - _{(offset)})/V_{Rc}$$

(6)

由於 $|_{(Rsense)}$ =|ref/10,因此可以估算滿載時的 $|_{Re2}$ :

$$I_{Re2(full\ load)} \approx 1.1 \times I_{ref}$$

(7

在最大負載電流下, Vout-的滿量 程值約為:

$$Vout-_{(fullscale)}-Vout-_{(offset)}$$

$$\approx Rc1 \times I_{Rsense(full load)}$$

(8)

採用LTspice電路模擬軟體產生圖

圖4:反轉Vout-消除了偏移,將輸出調整到所需範圍,並可以過濾輸出端的電源波紋或 負載尖峰。

圖5:將圖4中25nF的電容C1去掉後的Vout。

圖6: 圖4中加上25nF電容C1時的Vout。

圖7:主動設備上的電壓。

5、圖6和圖7的曲線,以顯示電路工作期間的線性度、濾波效果,以及Vce和Vds。負載電流從0增加到1安培,輸出電壓疊加在負載電流上,其結果

與實際的電路性能非常接近。由於負載電流尖峰值持續時間短,濾波防止了跳閘。隔離雖可能沒有必要,但在設計高壓電路時應始終予以考慮。 **198**

## 內建AFE微控制器適用 高精確度量測設備

瑞薩電子(Renesas Electronics) 推出32位元RX微控制器(MCU)的 RX23E-A產品家族,將高精確度的 類比前端(AFE)和MCU結合在單一晶 片上。RX23E-A MCU專為製造測試 和量測設備應用產品而設計。此外, RX23E-A MCU是瑞薩第一款在無校正 下,就能夠提供優於0.1%精確度來測 量訊號的解決方案。

這款新型MCU實現最高等級的AFE精確度(偏移漂移:10nV/°C、增益漂移:1ppm/°C、RMS雜訊:30nVrms),這種水準在以往只能透過結合運用高精確度運算放大器IC的專用A/D轉換器電路來達成。瑞薩藉由使用相同的製造製程技術,將這種高精準度AFE IP整合在單一晶片上,現在可以在單晶片上,實現高精確度感測器的量測、運算、控制和通訊。

由大數據所帶動的品質和生產力改良,讓工廠和生產基地面臨壓力,而必須準確可靠地測量各式各樣感測器的資料。由於使用者在各種環境溫度下以高精確度測量小訊號時,要求的是穩定性,因此將雜訊特性和溫度漂移特性降低到較低的水準非常重要。瑞薩為了滿足這些需求,開發高精準度AFE,並將其整合到RX MCU中。

瑞薩電子: www.renesas.com

#### eSPI到LPC橋接器保護既有投資

隨著工業運算產業逐漸從低接腳數 (LPC)轉為增強型串列周邊介面(eSPI) 匯流排技術,開發人員面臨將現有設 備更新為新標準所需的高開發成本。

為了讓開發人員能夠採用eSPI標

準,同時保留對傳統LPC設備的大量 投資,Microchip Technology推出 業界首款商用eSPI-to-LPC橋接器。 ECE1200橋接器使開發人員能夠在具 有傳統LPC連接器和周邊設備的電路 板中實施eSPI標準,大幅降低開發成 本和風險。

由於需要大量的前期投資,因此產品壽命在工業運算設備應用中至關重要。ECE1200 eSPI-to-LPC橋接器允許開發者維持生命週期的同時,支援採用新一代晶片組和CPU的新運算應用所需的eSPI匯流排技術。為降低開發人員的風險,eSPI匯流排技術經過工業運算應用的強力驗證,並已與領先的處理器公司進行了共同驗證。

Microchip: www.microchip.com

#### 三款Flash控制器瞄準廣泛應用 族群

衡宇科技(StorArt)宣佈將在2019年下半年將推出三款快閃記憶體(Flash)控制晶片,eMMC/SA3635、SSD/SA3811,以及uSD/SA3309。全系列產品直接瞄準了廣泛的應用族群,支持所有主流廠商的2D與3D-NAND Flash。

SSD控制晶片不僅通過PCIe logo、UNH-IOL、NVMe等國際認證,AES 256安全性演算法也通過美國商業部NIST的認證。SSD控制晶片SA3811,支援PCIe 3.0 × 4通道,和先進的NVMe 1.3技術,傳輸效能可高達4Gbps。

eMMC/eMCP控制晶片為全球數一數二有能力可支援TLC的eMMC/eMCP控制晶片,並通過全球各主流手機及平板電腦驗證,列入官方建議

採購名單。SA3635為eMMC5.1控制 晶片,內建32bit CPU並支援HS400高 速介面,支援全球NAND大廠全系列 Flash。SA3635搭配LDPC3I擎,加上專 利的AI演算法,配合豐富的量產經驗, 此eMMC解決方案可通過嚴苛的條件與 環境測試,提供客戶兼具可靠性、相容 性與優越讀寫效能的最佳選擇。

衡宇科技: www.storart.com.tw

#### 大幅降低漏地電流提高工廠可 用性

在變速驅動器中的個別元件會產生漏電流,而這些漏電流的累加會導致RCD設備跳閘。為此,TDK推出愛普科斯(EPCOS)LeaXield主動漏電流濾波器。這種新穎的解決方案可顯著降低漏電流,讓用戶能有效利用RCD設備並提高工廠的可用性。

一個完整的驅動系統包括EMC輸入濾波器、變頻器和馬達。這類驅動系統中容易被忽視但同樣重要的元件是變頻器與馬達之間的屏蔽電纜,其長度通常可超過200m。出於安全考慮,驅動系統通常採用RCD設備連接到電網。

例如,用於變速驅動器的標準RCD,對於頻率範圍在100Hz以下的電流具有30mA的跳閘閾值,當頻率大於100Hz時,跳閘閾值將顯著上升。典型RCD跳閘閾值,當頻率大於1kHz時,跳閘閾值約為300mA,變頻器開關頻率引起的可變漏電流可能會超過300mA跳閘閾值。在這些漏電流的共同影響下,系統會發生意外停機,從而導致工廠停工。

TDK: www.tdk.com

2019年11月7-8日

## 連接我們的世界

ASPENCORE 全球高科技領袖論壇

### 全球雙峰會:

全球 CEO 峰會 全球分銷與供應鏈領袖峰會

#### 同期舉辦:

全球電子成就獎 全球電子元器件分銷商卓越表現獎 展覽及技術應用課程

#### 已確定參加CEO峰會嘉賓(部分)

- Dr. Wei Shaojun, President, IC Design Branch, China Semiconductor Industry Association

- Aart de Geus, President & CEO, Synopsys

- Hassane El-Khoury, CEO, Cypress

- Alexander Everke, CEO, ams

- Nigel Toon, CEO, Graphcore

- Derek Meyer, CEO, Wave Computing (/MIPS)

- Jean-Christophe ELOY, President and CEO, Yole Développement

- Tomomitsu Maoka, senior Vice president & deputy general manager of Production and Technology Unit of Renesas

### 電子業界年度重磅大獎

【誠邀評選提名】

#### 全球電子成就獎

編輯推薦獎 企業獎 創新產品獎

#### 全球電子元器件分銷商卓越表現獎

年度最佳分銷商 三大供應鏈服務公司 年度傑出管理者 年度突出表現元器件分銷企業

#### 全球電子成就獎

全球電子成就獎評選並表彰對推動全球電子產業創新做出傑出貢獻的企業和管理者。由 ASPENCORE 全球資深編輯組成的評審委員會以及來自亞、美、歐洲的 ASPENCORE網站用戶共同評選出得獎者。

#### 全球電子元器件分銷商卓越表現獎

獎項創辦於 2001 年,備受業界推崇,旨在表彰支援電子 產業發展的卓越品牌分銷商。評選結果深受電子製造商 信賴,是他們挑選分銷商合作夥伴的重要參考。

提名時間: 2019年4月5日-8月16日

獎項名稱、評選細則及獲取提名表請聯繫:Angel.Heldaspencore.com

合作諮詢請聯繫:marketing.success@aspencore.com

主辦方:

**ASPENCORE**

大會媒體:

ASPENCORE

7010

World Hacronics Achievement Awards

Awards

全球电子成就奖

**頒獎盛典** 11月7-8日•深圳

## 2019 感測與無線融合技術沙龍

2019 年 8 月 • 台北文華東方酒店

#### 參與廠商:

還有更多廠商陸續加入

#### 主辦單位:

EDNI電子技術設計

#### 會議諮詢

Rebecca.Shih@aspencore.com +886 2 2759 1366#103

#### 更多研討會資訊

FB 粉絲頁